第一章 FPGA時序約束分享03_input delay約束

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?作者:潘文明

? ?本文章探討一下FPGA的時序input delay約束,本文章內容,來源于配置的明德揚時序約束專題課視頻。

?《FPGA時序約束分享01_約束四大步驟》概括性地介紹 了時序約束的四個步驟,對時序約束進行了分類,并得到了一個分類表。

?《FPGA時序約束分享02_時鐘約束》詳細介紹了關于時鐘的約束,根據時鐘來源可以分成輸入時鐘約束、PLL等衍生時鐘約束和自己分頻的時鐘約束等三種類型。這三種類型的約束方法均有所不同,讀者需要掌握區分方法。

? 本文,筆者將詳細介紹輸入延時(input delay)的概念、場景分類、約束參數獲取方法以及約束方法。

? 在高速輸入設備與FPGA通信場合,設置輸入延時(input delay)約束非常重要。

? 例如明德揚研發的高速ADC模塊:mdyFmcAd9653,該模塊集成了2個125M采樣率、分辨率為16位的AD9653,采集數據時通過LVDS傳輸至FPGA上。該LVDS的時鐘頻率為125M,數據位寬為16位,FPGA接收時,需要進行輸入延時(input delay)約束,將LVDS時鐘和數據的相位關系告知FPGA,從而讓FPGA能夠正確接收,如果約束不正確,則會出現接收錯誤的情況。

? 還有一個常用場景,就是網絡芯片的RGMII接口。RGMII接口用于網絡芯片和FPGA之間的網絡數據傳輸,網絡芯片往FPGA發數據,即FPGA接收數據時,就需要設置輸入延時(input delay)約束。RGMII接口務必要做時序約束,否則會出現偶發性的數據接收錯誤的情況,筆者在做“弱小信號采集系統項目”時,就在這里吃過虧。

? 開始正文,首先討論并明確輸入延時(input delay)的概念。

?

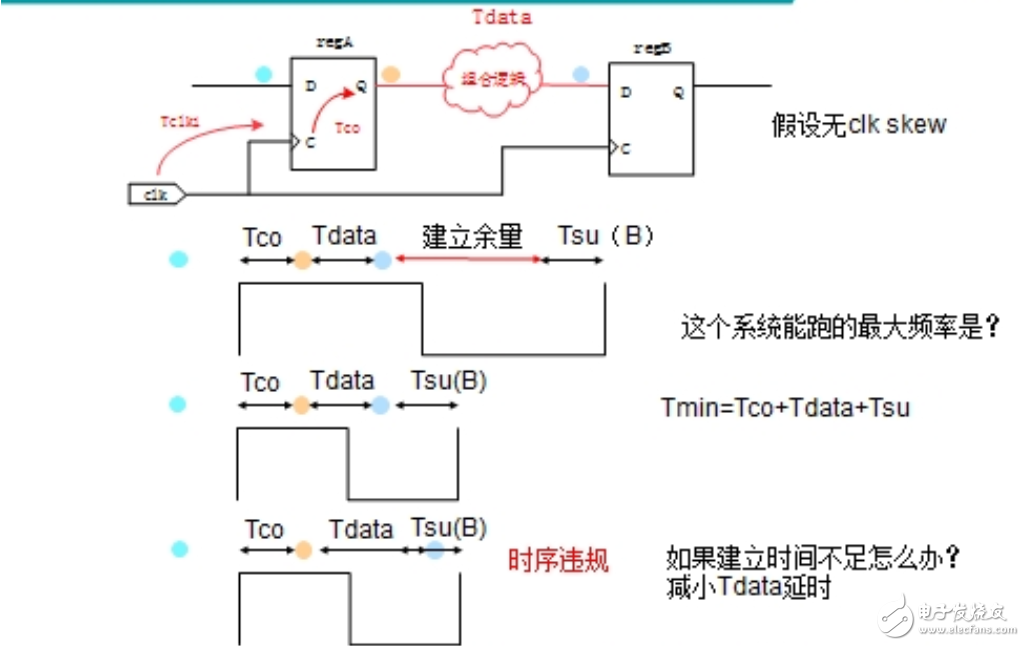

第1節 輸入延時概念

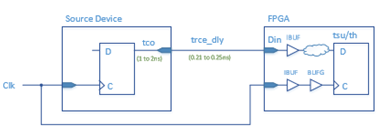

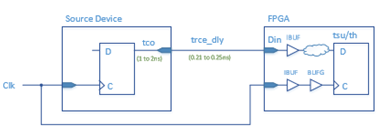

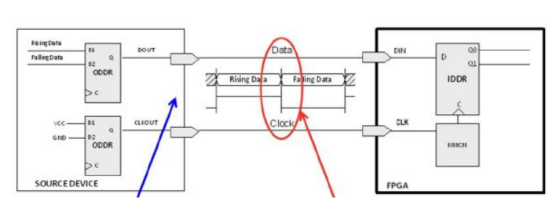

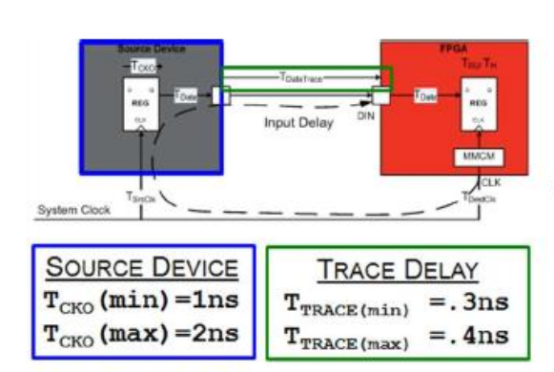

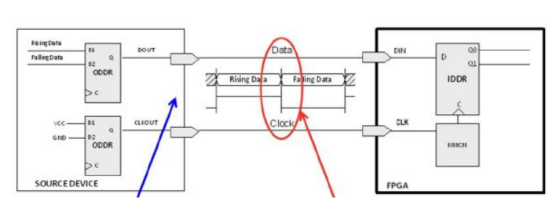

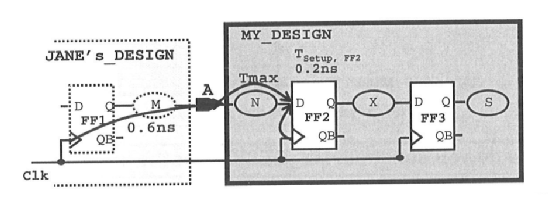

上圖是一個典型的輸入延時的模型,該模型由一個上游器件source device以及一個FPGA組成。上游器件將數據傳送給FPGA,FPGA接收數據。從FPGA角度來看,輸入接口由時鐘接口和數據接口組成,上圖右邊FPGA的輸入管腳,上面即是數據接口,下面是時鐘接口。

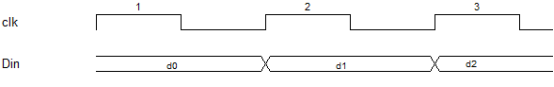

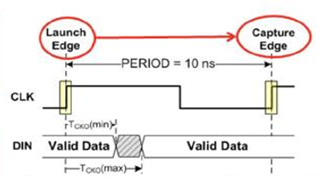

Din是由時鐘clk產生的,理想情況下,Din的變化時刻一定是時鐘的上升沿,即變化點和時鐘上升沿對齊,如上圖所示。

但在傳輸過程中,由于時鐘和數據會存在延時差異,從而到達FPGA管腳是處于不同的時刻,數據和時鐘之間會存在相位差,如下圖所示。

上圖描述了連續3個時鐘下,數據接口din和時鐘clk的相位差,第1個時鐘相差了1ns,第2個時鐘差了1.8ns,第3個時鐘相差了1.3ns。相位差的變化有可能是延時原因,也有可能是上游器件的原因,總之,這些相位差數據是變化的,但它的變化應該在一個確定的范圍,即肯定是存在一個最小值,同時存在一個最大值,相位差在這兩個范圍內變動。

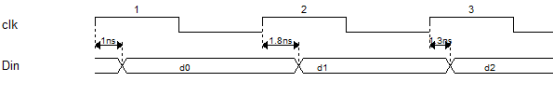

將其變化范圍匯總起來,制作成如下的一張圖。

上圖中的灰色區域,就是相位差的變化范圍。

現在可以給出輸入延時(input delay)的定義:數據相對于時鐘的延時,即數據時間-時鐘上升沿時間。

a.注意是數據時間-時鐘上升沿時間,這意味著輸入延時可正可負。當延時在時鐘右邊時,輸入延時是正的,當延時變化點在時鐘上升沿左邊時,輸入延時是負的。

b.輸入延時通常是一個變化范圍,其有兩個參數,最小延時min和最大延時max。最小延時即上圖中灰色區域最左邊點,最大延時是灰色區域最右邊點。

c.輸入的實際延時一定在最小和最大之間。約束時,需要設置好最小min和最大max的值。

d.上圖中的clk和din是指FPGA管腳的,非上游器件管腳的。

e.牢記輸入延時的概念定義,后面場景無論如何變化,萬變不離其宗,都是按這個定義約束的。

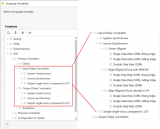

第2節 約束語句

設置輸入延時的約束語句,其語法非常簡單,如下

set_input_delay -clock

?是想要設定input約束的端口名,可以是一個或數個port。

?-clock之后的clock_name,是時鐘域的名字。

?注意,這個clock_name是設置約束約束時定義的時鐘域的名字,而非“時鐘”名。

?可以是一個真實存在的時鐘

?也可以是預先定義好的虛擬時鐘

?delay分兩種

?-max ,輸入的最大延時,用于建立時間setup的分析,具體原因看后面部分。

?-min ,輸入的最小延時,用于保持時間hold的分析,具體原因看后面部分。

下面是具體的兩個例子

set_input_delay -clock [get_clocks clk0] -min 0.5 [get_ports Din[*]]

set_input_delay -clock [get_clocks clk0] -max 1.5[get_ports Din]*]]

上面約束了信號Din相對于時鐘域clk0,有最小延時0.5和最大延時1.5ns。

第3節 輸入延時的目的

請繼續看上面的輸入延時的模式,注意看FPGA的內部結構。上游器件將數據發到FPGA的輸入管腳,FPGA對其進行采樣,采樣一定會使用到D觸發器,所以輸入的時鐘和數據,最終均會連到FPGA內部的D觸發器上。

由前面幾篇文章的討論可知,D觸發器是有建立時間和保持時間要求的。這個建立時間和保持時間,是這個D觸發器的物理特性,是一定會有的,但這個數值是多少,工程師不知道,而綜合工具如VIVADO、QUARTUS等會知道。

當Din和clk的延時不滿足D觸發器的建立時間和保持時間時,綜合工具自動調整內部延時,例如增加一些BUF,或者增加線長等方式,使得信號最終到達D觸發器時,能夠滿足建立時間和保持時間的要求。

所以綜合工具需要知道輸入的延時是多少,進而調整內部延時,最終滿足D觸發器的建立時間和保持時間要求,這就是設置輸入延時的目的。

有幾點需要注意的。

a.設置輸入延時,只是客觀描述外部信號,即數據和時鐘和相位關系。只要知道綜合工具這種相位關系,剩下的調整是綜合工具自動完成的。

b.雖然綜合工具可以調整內部延時,從而達到內部D觸發器正確采樣的目的,但這個延時是有一定范圍的,存在無論怎么調都無法滿足的情況。

第4節 獲取參數的兩種方法

由本文的約束語句一節,可以知道為了設置輸入延時約束,需要知道兩個參數:最大延時值max和最小延時值min。

那我們一般如何獲取這兩個參數呢?有兩種方法,一種是查閱數據手冊,另一種是通過示波器測量。

?

4.1 查閱數據手冊

數據和時鐘的相位偏差,通常來自于上流器件的寄存器延時和走線延時。

一個正規的器件,其數據手冊會清楚地標明輸出數據和時鐘的延時范圍,通常是寄存器延時TCKO等,大家可以查找一下。

至于走線延時,通常可以通過線長度,計算得到延時值。

所以第一種方法,就是查閱數據手冊,獲取時序參數,具體如何使用,可以看后面內容。

?

4.2 示波器測量

第二種方法是示波器測量的方法。

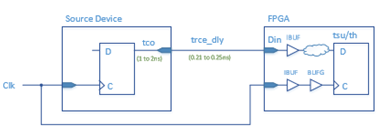

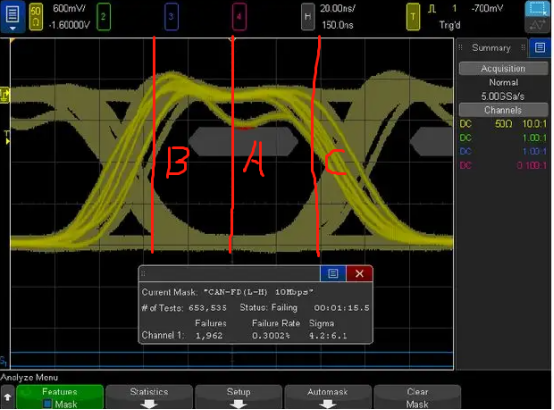

方便的話,使用示波器接到FPGA的輸入的時鐘和數據管腳,調整示波器處于眼圖模式,就可以得到眼圖,其樣式大致如下。

上圖是按照時鐘基準來獲取到的眼圖,從上圖就可以得到數據相對于時鐘的延時信號,從而得到max和min值。

知道了上面兩種方法后,還要結合應用場景,才能正確地設置時序參數。

第5節 應用場景概念

?

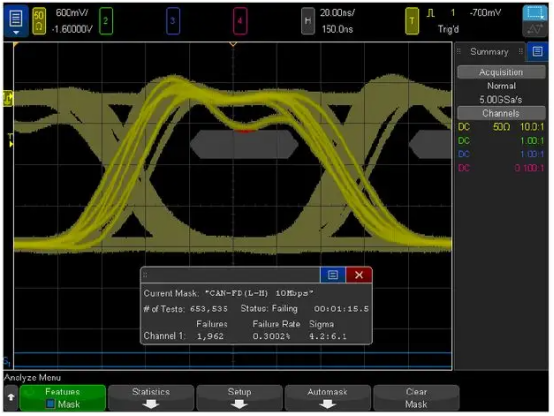

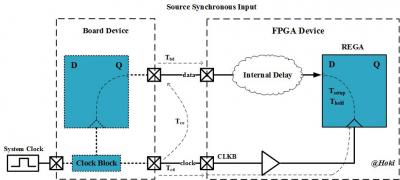

5.1 系統同步和源同步

數據接口的同步方式,分成系統同步和源同步。

系統同步是指板上有一個時鐘源,該時鐘源將時鐘送給各個器件,并且保證送給各個器件 的相位是相同的。如上圖中,時鐘system_clock送給了source device和FPGA,并且兩者時鐘TsrcClk和TdstClk相位是一樣的,上游器件只發數據給FPGA即可。

系統同步要求時鐘信號在系統級上同源,板級走線的延時也要對齊,要求很高,也比較難做。

?

源同步如上圖,FPGA的時鐘來自于上游器件 ,即上游器件將數據送給FPGA的同時,送一個隨路時鐘給FPGA,FPGA利用這個隨路時鐘來采樣數據。源同步方式,沒有時鐘相位同步的要求,所以相比系統同步簡單很多,應用也更加廣泛。

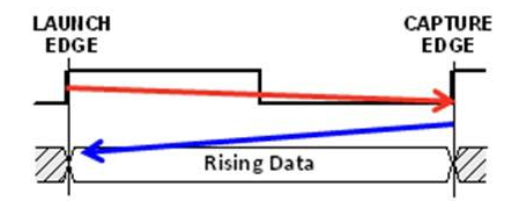

SDR是指數據只在時鐘上升沿有效,當前時鐘上升沿產生數據,在下一個時鐘上升沿對這個數據進行采樣的方式,上圖就是SDR的示例。

DDR是指數據在時鐘上升沿和下降沿都有效的一種傳輸方式。時鐘上升沿產生的數據,在下一個時鐘下降沿被采樣;時鐘下降沿產生的數據,在下一個時鐘上升沿被采樣。

由引可見,同樣時鐘頻率下,DDR的速率是SDR的兩倍,速率更高,要求自然也更高。

系統同步由于要求時鐘信號在系統級上同源,板級走線的延時也要對齊,無法達到更高速的設計要求,所以大部分情況也僅僅應用SDR方式,本文針對系統 同步,只討論SDR的方式。

源同步接口最大的優點就是大大提升了總線的速度,可以是SDR方式,也可以是DDR方式,本文針對源同步,將討論

SDR和DDR兩種方式。

?

5.3 中心對齊和邊沿對齊

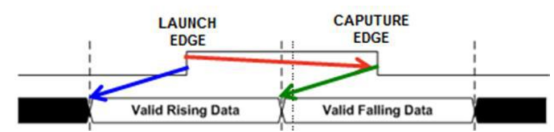

在DDR的傳輸方式中,我們又可以分成中心對齊和邊沿對齊兩種方式。

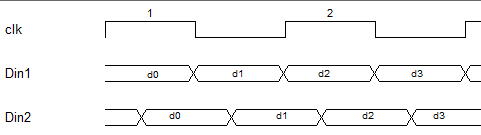

上面是FPGA收到的一個理想的傳輸波形圖。Din1的變化點與時鐘clk的邊沿點對齊,這種傳輸方式就是邊沿對齊。Din2的變化點則是在clk的低電平或者高電平中間,這種傳輸方式就是中心對齊。

上圖是一個理想的波形,是假設Din1和Din2 零延時的情況,但實質上這是不可能的。在實際中,必會有延時,而且必定會有抖動,這個抖動圍繞著數據變化點可能向左偏,也可能向右偏。由此,邊沿對齊的實質波形如下圖(在時鐘邊沿左右抖動,中間穩定)。

同理,中心對齊的實質波形將如下圖所示(時鐘邊沿處穩定,中間抖動)。

第6節 各種場景下的約束方法

經過前面的鋪墊和討論,現在正式討論各個應用場景下,輸入延時的約束方法。

?

6.1 系統同步

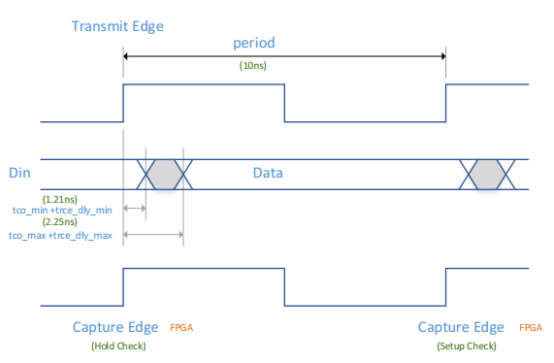

系統同步的特點是時鐘到各個器件的延時是一樣的,這意味著設置輸入延時時,不需要考慮時鐘的延時,可以認為時鐘延時是0,我們只需要考慮數據延時。

數據延時為兩種,一種是上游器件在時鐘控制下將數據輸出到上游器件管腳的延時;另一種是數據從上游器件管腳,到FPGA管腳的延時。

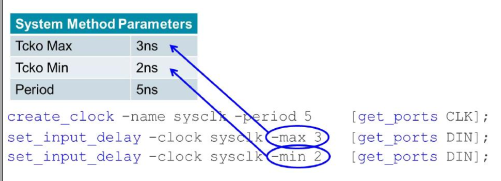

?查閱數據手冊

假設通過查閱數據手冊,得到TCKO最小是1ns,最大是2ns;通過計算布線長度,得到線延時最小是0.3ns,最大是0.4ns。由此可計算得到,輸入最小延時:最小的TCKO+最小的線延時,即1.3ns;輸入最大延時:最大的TCKO+最大的線延時,即2.4ns。所以可以有如下約束語句。

set_input_delay -clock sysclk -min 1.3 ?[get_ports Din]

set_input_delay -clock sysclk -max 2.4 [get_ports Din]

?示波器測量

如果您找不到數據手冊,或者電路板做得不標準,也可以使用示波器測量方法得到參數。假設眼圖如下:

上圖中,中間的A處是時鐘上升沿時刻,B處是眼圖閉合的左側,C處是眼圖閉合的右側。從示波器中,可以得到B到A的距離,以及C到A的距離。而這兩個距離,則正對應輸入延時的最小值和最大值。如下圖,圖中的灰色區域,就是上圖中的B到C的區域。

?

如前面所述,系統同步要求較高,大部分都是SDR情形,所以不在此討論DDR的情節。

6.2 源同步SDR

源同步SDR的約束方法,與系統同步非常相似。

源同步是上游器件同時傳輸了時鐘和數據,如果布線做得標準的話,即線等長的話,可以認為數據延時和時鐘延時是一致的,也就是說我們可以不考慮線延時的情況。

所以通過數據手冊,查詢 到TCKO延時,就可以設置最大最小值了。

通過示波器測量,也可以獲取到參數,下圖就是眼圖。

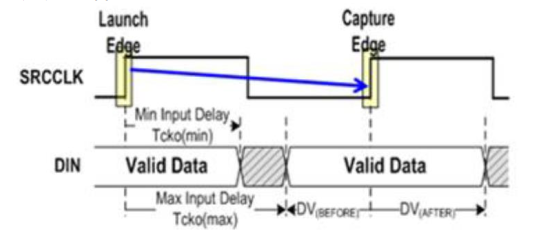

上圖中,A是時鐘上升沿處,B是眼圖的左側,定義為DV(befre),C處是眼圖的右側,定義為DV(altera),這兩值都可以測量到。

上圖是對應的波形圖。

如何通過DV(befre)和DV(altera),獲取到最小延時和最大延時呢?

認真觀察,可以知道,最小延時就是DV(after);而最大延時則要計算一下,時鐘周期-DV(before)。

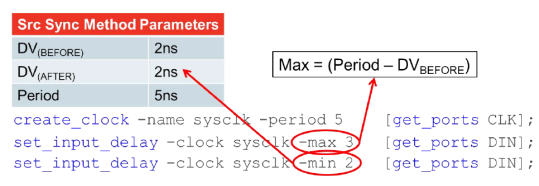

下面就是一個配置的例子。

6.3 源同步-DDR

討論完成源同步的SDR,接下來討論源同步的DDR情形。源同步的DDR是時鐘上升沿和下降沿都會采數據的情況,可以進一步劃分成中心對齊和邊沿對齊情形。

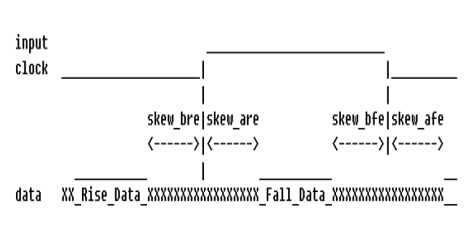

6.3.1 DDR中心對齊

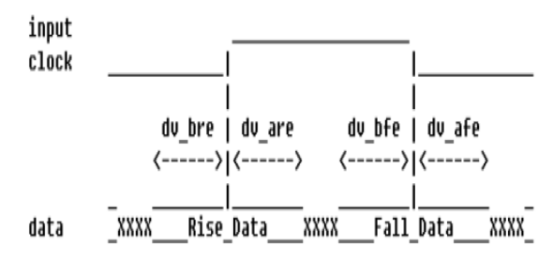

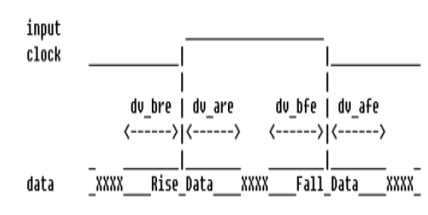

上圖是DDR中心對齊的波形圖,其中有4個參數可以通過示波器得到,分別是上升沿前dv_bre、上升沿后dv_are、下降沿前dv_bfe和下降沿后dv_afe。

注意,上圖中,Fall_Data是由時鐘上升沿產生,在時鐘下降沿采樣的;Rise_Data是由時鐘下降沿產生,時鐘上升沿采樣的。

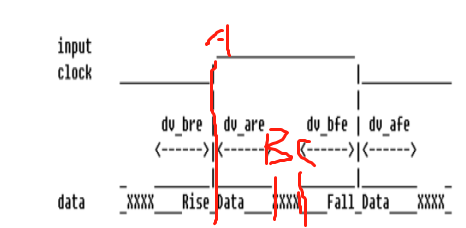

根據輸入延時的定義,上升沿的輸入最小延時是上圖中的B到A的時間;輸入最大延時是上圖中的C到A的時間。因此,可知上升沿輸入最小延時等于:dv_are;上升沿輸大最小延時等于:半個時鐘周期-dv_bfe。

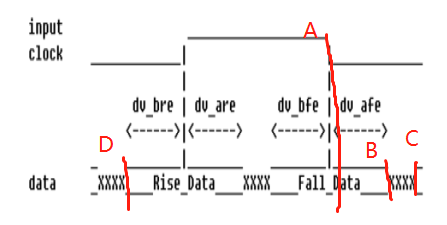

下降沿的情況看上圖。根據定義,下降沿的輸入最小延時是B到A的時間;下降沿輸入最大延時是C到A的時間。注意,根據周期性,上圖中的C和D是相同的點。

可此可知,下降沿的輸入最小延時是dv_afe;下降沿輸入最大延時是:半個時鐘周期-dv_bre。

現在舉例說明,假設

?時鐘的頻率為:100M,即周期為10ns;

?數據data的dv_bre:0.4ns

?數據data的dv_are:0.6ns

?數據data的dv_bfe:0.7ns

?數據data的dv_afe:0.2ns

則有,上升沿的輸入最大延時:半個時鐘周期-dv_bfe=4.3ns;上升沿的輸入最小延時:dv_are=0.6ns;下降沿的輸入最大延時:半個時鐘周期-dv_bre=4.6ns;下降沿的輸入最小延時:dv_afe=0.2ns;

可以列出出如的約束語句:

set_input_delay -clock clk -max 4.3 [get_ports data]

set_input_delay -clock clk -min 0.6 [get_ports data]?

set_input_delay -clock clk -max 4.6 [get_ports data] -clock_fall -add_delay

set_input_delay -clock clk -min 0.2 [get_ports data] -clock_fall -add_delay

上面的語法中,使用-clock_fall表示下降沿;使用-add_delay表示與前面的約束一起生效。

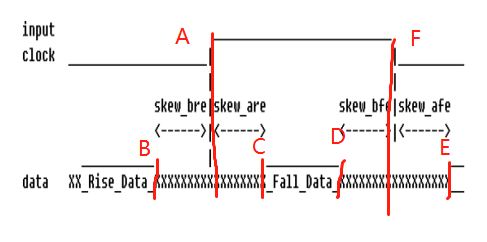

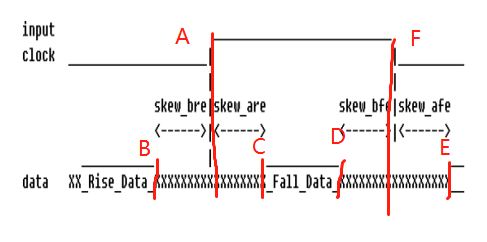

6.3.2 DDR邊沿對齊

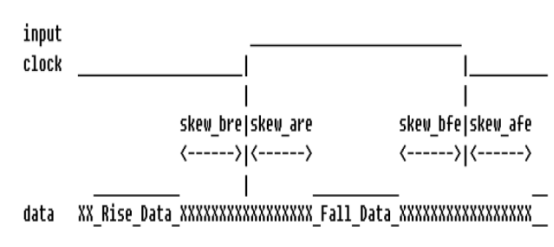

上圖是DDR中心對齊的波形圖,其中有4個參數可以通過示波器得到,分別是上升沿前skew_bre、上升沿后skew_are、下降沿前skew_bfe和下降沿后skew_afe。

注意,上圖中,Fall_Data是由時鐘上升沿產生,在時鐘下降沿采樣的;Rise_Data是由時鐘下降沿產生,時鐘上升沿采樣的。

根據輸入延時的定義,上升沿的輸入最小延時是上圖中的B到A的時間;輸入最大延時是上圖中的C到A的時間。有讀者會疑問,為什么不是D和E呢?注意一下輸入延時的定義,是“產生的數據”到“產生該數據的時鐘沿”的距離。Fall_data是由A產生的,B到C區域,都是Fall_Data的變化區域,所以應該看的是B和C到A的距離 。這個時候,B在A的左邊,說明該值是負數。

理解了上面的定義,可知上升沿輸入最小延時等于:-skew_bre;上升沿輸入最大延時等于:skew_are。

下降沿的情況看上圖。根據定義,下降沿的輸入最小延時是到D到F的時間;下降沿輸入最大延時是E到F的時間。

可此可知,下降沿的輸入最小延時是:-skew_bfe;下降沿輸入最大延時是:skew_afe。

現在舉例說明,假設

?時鐘的頻率為:100M,即周期為10ns;

?數據data的skew_bre:0.6ns

?數據data的skew_are:0.4ns

?數據data的skew_bfe:0.3ns

?數據data的skew_afe:0.7ns

則有,上升沿的輸入最大延時:skew_are=0.4ns;上升沿的輸入最小延時:-skew_bre=-0.6ns;下降沿的輸入最大延時:skew_afe=0.7ns;下降沿的輸入最小延時:-skew_bfe=-0.3ns;

可以列出出如的約束語句:

set_input_delay -clock clk -max 0.4 [get_ports data]

set_input_delay -clock clk -min -0.6 [get_ports data]?

set_input_delay -clock clk -max 0.7 [get_ports data] -clock_fall -add_delay

set_input_delay -clock clk -min -0.3 [get_ports data] -clock_fall -add_delay

上面的語法中,使用-clock_fall表示下降沿;使用-add_delay表示與前面的約束一起生效。

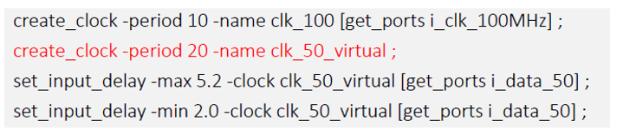

6.4 有數據無時鐘

? ? ? 有一種特殊的輸入信號,該信號是沒有對應的時鐘,是一種異步信號。例如最常見的UART串口信號,上位機發給FPGA只有一根線,雙方按照約定的波特率進行通信。

FPGA使用內部的時鐘去采這個異步信號,由于時鐘和信號是異步的,因此無論怎么調整,都不能保證一定能夠滿足D觸發器的建立時間和保持時間要求,這個時候要做異步信號同步化處理后,才能采集,否則會出現亞穩態現象,嚴重的會導致芯片崩潰。關于這部分內容,可以看時序約束的其他章節。

本文要探討的是,對于這種異步信號,需不需要做輸入延時的約束呢?

答案是需要的。對其進行時鐘約束,其主要目的不是為了調整延時,而是為了告訴綜合工具,這個信號是處于不同時鐘域的,避免被系統認為屬于某一時鐘域,從而不產生警告,進而導致工程師遺漏了此問題的解決。

由于異步信號沒有時鐘,因此我們需要構造一個虛擬時鐘,如以下語句,就是產生了一個50M的虛擬時鐘clk_50_virtual,注意該語句并沒有關聯任何端口,所以是虛擬的;還要注意的是,定義為50M是隨便的,您可以定義為其他任何頻率。

create_clock -period 20 -name clk_50_virtual

當構造了虛擬時鐘了,就可以設置異步信號的輸入延時了,例如下面語句。注意5.2也是任意的。

set_input_delay -max 5.2 -clock clk_50_virtual [get_ports i_data]

第7節 總結與建議 ??

最后,對本文進行簡單的總結 。

a.本文先介紹 了輸入延時的概念,然后分成不同的應用場景,根據這些應用場景不同,分別使用不同的約束方法。

b.輸入延時約束關鍵的是獲取約束參數,可分成查閱數據手冊和示波器測量方法。

c.輸入延時約束,只是客觀反映外部信號的情況,千萬不要理解成“要求系統,讓輸入延時多少ns”。即不是要求系統做什么,而是告訴系統輸入信號的情況,而系統決定怎么做。

第8節 相關產品 ??

本文提到的mdyFmcAd9653,是由明德揚科教研發的多通道,高分辨率和高采樣率數模轉換器的ADC系列子板,搭載兩片ADC芯片,支持ADI、上海貝嶺、北京時代民芯科技、中電24所等生產的芯片,完全PIN對PIN兼容;共支持8通道同步輸入;共支持16位采樣分辨率;支持最高125MSPS的采樣率,適用于醫療電子、雷達、衛星導航等多種應用場合。

?

第9節 相關文章 ??

1.《FPGA時序約束分享01_約束四大步驟》

2.《FPGA時序約束分享02_時鐘約束》

3.《mdyFmcAd9653產品說明書》

?

電子發燒友App

電子發燒友App

評論