在網絡技術應用日益廣泛的今天,網絡傳輸是最經濟有效的數據傳輸方式。如何利用廉價的51單片機來控制網卡芯片進行數據傳輸,加載TCP/IP協議連接到互聯網,實現網絡通信成了眾多設計者的目標。但由于指令

2021-07-21 07:31:53

數據傳輸模塊

2024-03-15 10:23:31

CPLD程序如何去實現?CPLD在通信數據傳輸中的應用是什么?

2021-05-25 06:53:01

看到一個公式,數據傳輸率:13.56MHZ/128 = 106Kbit/s;其中13.56MHZ是載波頻率,為什么要除以128,數據傳輸速率和載波頻率有什么關系?

2023-05-10 17:13:18

一、數據傳輸指令───────────────────────────────────────它們在存貯器和寄存器、寄存器和輸入輸出端口之間傳送數據.1. 通用數據傳送指令.MOV 傳送字或字節.MOVSX 先符號擴展,再傳送.MOVZX 先零擴展,再傳送.PUSH 把字壓入堆棧.POP 把字...

2021-07-27 07:18:33

數據傳輸指令有何作用?數據傳輸指令有哪幾種?算術運算指令有哪幾種?邏輯運算指令又有哪幾種呢?

2021-10-15 09:51:17

之前嘗試用ARM LPC1768的8個引腳作為數據輸入端口,將CLPD的8個引腳作為數據輸出端口,直接進行降CPLD中數據送入到LPC1768中,在調試過程中,發現將CPLD中數據直接通過8個引腳

2013-08-04 14:10:23

原先的總線矩陣+仲裁器結構中的數據總線進行數據傳輸的?

接上一個問題,如果是的話,那么當進行DMA數據傳輸時,必定是需要占用數據總線的,那么此時CPU在干嘛呢?它是否需要等待數據總線空閑才能進行它

2023-05-25 17:18:32

1 引 言 隨著市場上對無線數據業務的需求日益增多,運營商紛紛大力發展自身領域內的數據服務,力求在激烈的競爭中占得先機。傳統的GSM網絡僅能支持9.6 kb/s速率的數據傳輸業務,這遠遠不能

2019-07-05 06:05:11

ROHM公司日前研發了高速數據傳輸方式的Ir Simple-4M規格的控制器LSI,據稱其速度相當于現行IrDA標準傳輸(IrDA-115k方式)速度的50倍,數據傳輸速率為IrDA-4M方式的4

2018-11-19 16:51:08

引言在一般的項目開發過程中,往往需要兩塊或以上單片機進行通信完成數據傳輸,例如四旋翼無人機在飛行過程中無線傳輸數據回到地面站,治療儀器需要實時將患者和機器運轉情況傳回上位機平臺,糧倉溫控裝置需將各種傳感器通過RS485總線...

2021-08-23 07:52:34

引言在一般的項目開發過程中,往往需要兩塊或以上單片機進行通信完成數據傳輸,例如四旋翼無人機在飛行過程中無線傳輸數據回到地面站,治療儀器需要實時將患者和機器運轉情況傳回上位機平臺,糧倉溫控裝置需將各種

2021-08-23 07:16:26

傳輸數據。與逐字節數據傳輸模型不同,讀/寫數據模型可以處理數據塊;c)使用緩沖隊列傳輸模型——允許客戶端對數據傳輸進行隊列處理。考慮到前面提到的每個模型的最佳應用是什么?在第一種方法中,我嘗試使用第一個

2020-04-23 13:56:48

實現數據通信。在USB數據傳輸的設計方案中采用PDIUSBD12芯片作為USB控制器。PDIUSBD12完全符合USB1.1版規范;同時它還符合大多數器件的分類規格;還適用于許多外設,如打印機、掃描儀、外部

2019-06-17 05:00:10

gprs數據傳輸流程是怎樣的?

2022-02-09 07:28:44

labview 遠程數據傳輸

2013-07-04 19:30:55

labview數據傳輸注意事宜,很好的總結

2017-03-30 21:15:19

我是在能采集溫度數據的PC上做已有軟件的二次開發,用它的開放端口把數據傳輸到我的labview上,它自帶的通訊協議上說開發端需要開啟TCP服務,監聽端口,等待PC端主動發送請求并處理通訊會話。但是我

2017-10-11 18:44:31

引言在一般的項目開發過程中,往往需要兩塊或以上單片機進行通信完成數據傳輸,例如四旋翼無人機在飛行過程中無線傳輸數據回到地面站,治療儀器需要實時將患者和機器運轉情況傳回上位機平臺,糧倉溫控裝置需將各種

2021-08-23 07:32:59

申請理由:飛凌嵌入式OK210開發板是很好的開發板,我很希望能得到這個開發板并通過它來學習更多知識項目描述:內容:(1) 針對系統的需求選擇合適的無線數據傳輸模塊。(2) 根據選擇的器件設計外圍電路

2015-07-24 10:39:33

實驗時,偶爾出現數據卡頓現象,界面通信受到干擾,實際下位機在正常工作,過一會又可以自行恢復,有沒有什么可以提高數據傳輸速率的方法,或者定時清除傳輸數據緩存?

2020-04-11 14:37:32

串口通信中外設與開發板串口通信是如何進行數據傳輸的?在使用外設時怎樣將外設的數據返回給開發板呢?

2021-07-07 07:58:07

本章以AN3485模塊介紹RS485的數據傳輸。

2021-02-26 07:28:54

信號采集系統中的數據傳輸顯示與處理

2012-05-12 22:25:25

隨著存儲技術的迅速發展,存儲容量得到了迅速的增長,存儲系統的數據傳輸速度成為了主要的瓶頸。光纖的傳輸具有其速度上的優勢,然而,在光纖傳輸要受到光纖通道接口的限制,因此光纖通道應用于高速數據傳輸的一個關鍵技術問題是接口的設計問題,本文對有效地解決高數據傳輸在接口處的瓶頸具有現實意義。

2019-08-22 08:06:39

單片機用于數據傳輸的外設有哪些?原諒在下孤陋寡聞,我所知道的有SPI、I2C,不知還有哪些?誰的數據傳輸速度最快?

2016-09-02 12:22:24

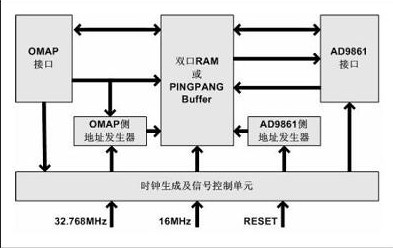

: 對于PingPong模式的數據傳輸,是否只是用一個channel進行數據傳輸?如果是,那么Ping PaRAM和Pong PaRAM中所設置的TCC是否是一樣的的?在使能中斷時,是否只需將IER中這一個

2018-06-20 06:05:34

圖像數據傳輸卡的原理是什么?圖像數據傳輸卡的實現方法是什么?

2021-06-04 06:51:18

22.4Gbps(Kintex-7).2. 1對LVDS接收時鐘+16對LVDS接收數據.本人可以提供FPGA源代碼.同時還可以在Xilinx評估板ML555/ML605/KC705上演示驗證.如有高速LVDS數據傳輸相關方面的技術合作,可聯系我。聯系方式:neteasy163z@163.com

2014-03-01 18:47:47

跪求基于labview的遠程數據傳輸的源代碼

2013-07-03 16:32:04

我們正在使用 IrDa 進行紅外數據傳輸。但是在 LPC54018 的用戶手冊中沒有提到 IrDa。請更新此控制器是否具有 IrDa 兼容性,否則我們如何進行此通信。在 LPC 1768 和 1788 中對 UART 協議中的 IrDa 應用有單獨的規定。

2023-03-21 06:19:46

終端之間的數據傳輸通過收發器進行,構成點對點無線數據傳輸系統。整個系統中,兩數據終端之間的無線通信采用433MH

2021-12-09 08:09:31

,這是不起作用的。令人驚訝的是,該設備甚至不引發任何中斷,也不使用端點緩沖器來進行數據ISO數據傳輸。此外,當我開始在PC中錄制時,設備發送空數據包,我不確定使用哪個數據緩沖區來進行數據傳輸。如果有

2019-03-26 13:10:04

無線數據傳輸系統的搭建和實際測試研究

2021-03-09 06:06:13

大家好:我正在學習使用 IEEE 802.15.4 中的 JN5169 來開發項目。我的項目基于JN-AN-1174。我已經實現了從EndDevice到Coordinator的數據傳輸,但是現在我

2023-03-24 08:38:45

的終端產品特性。在單端數據傳輸中,我們使用變壓器,初級繞組的一端接地。輸入信號中的邏輯轉換編碼為脈沖,相對于地面始終為正極性,位于發送器芯片上。這也稱為“一脈沖兩脈沖”,因為上升沿編碼為兩個連續脈沖,而

2017-04-13 14:35:46

本設計綜合實現了PC主機與DSP從機的RS-485遠距離通信接口和DSP從機與CAN現場總線的數據傳輸接口設計。

2021-06-03 06:52:41

在數字通信中的數據傳輸速率與調制速率是兩個容易混淆的概念。數據傳輸速率(又稱碼率、比特率或數據帶寬)描述通信中每秒傳送數據代碼的比特數,單位是bps。

2021-04-23 07:34:17

無線數據傳輸傳送收發遙控器dw-m11明的數據傳輸設備,代替有線的485通信,應用于電廠,鋼廠,碼頭,煤礦等工業場合,抗干擾能力強,性能穩定。線數據傳輸傳送收發遙控器,用于代替有線的485通信。采用

2013-07-08 14:29:35

無線數據傳輸是指利用無線數傳模塊將工業現場設備輸出的數據或者各種物理量進行遠程傳輸,可以進行無線模擬量采集也可以進行無線開關量控制,如果傳輸的是開關量,可以做到遠程設備遙測遙控。

2019-10-22 09:01:12

。由此可見,無線數據傳輸模塊的應用正在不斷擴展,市場前景是廣闊的,在無線數據傳輸模塊的實際應用中,和遠智能無線數據傳輸模塊也將不斷完善創新,發揮更大的優勢。

2019-06-18 04:21:52

目前,無線通信技術已經成為一大熱點,而系統設計的微型化、低功耗成為發展的必然趨勢。在保證系統工作可靠性的前提下,如何實現系統低功耗是無線數據傳輸系統亟待解決的一個主要問題。本文利用MSP430超低

2019-08-01 07:08:45

小弟正在做一項目,利用 STM32做的關于數據采集系統,打算利用USB實現和PC的數據傳輸,目前了解到的資料多是關于USB 讀寫U盤等存儲設備,請問關于USB數據傳輸的需要參考哪些資料?USB HID?普通的數據采集卡是如何通過USB接口和PC間實現數據傳輸的?

2017-07-06 22:02:00

的先進性,規定了同時使用這兩種接口實現數據通信。在USB數據傳輸的設計方案中采用PDIUSBD12芯片作為USB控制器。PDIUSBD12完全符合USB1.1版規范;同時它還符合大多數器件的分類規格;還

2018-12-04 10:37:41

的機會。 目前,藍牙是短距離無線數據傳輸領域的王者。然而,一個名為NFC的新競爭者最近從陰影中崛起,并積累了大量粉絲。風言風語,NFC是適合坐上寶座的新國王……但是是嗎? 在接下來的幾行中,我們將唱冰

2022-06-29 16:18:07

引言在一般的項目開發過程中,往往需要兩塊或以上單片機進行通信完成數據傳輸,例如四旋翼無人機在飛行過程中無線傳輸數據回到地面站,治療儀器需要實時將患者和機器運轉情況傳回上位機平臺,糧倉溫控裝置需將各種傳感器通過RS485總線或者CAN總線的方式達到數據傳輸的目的等等,這些...

2021-08-23 09:01:02

所示。 外部裝置通過音頻輸入輸出接口與智能終端進行數據通信,數據信號在主控模塊中進行編解碼處理,再通過控制裝置讀取、寫入外部介質,并存儲數據。數據傳輸的具體方式中,外設裝置通過插入手機外置話筒音頻輸入

2019-06-21 05:00:10

無線數據傳輸方式代替有線數據傳輸,則能很好地解決此類問題。綜上論述,文中提出一種基于高性能MCU和nRF24L01的網絡化無線通信系統的解決方案,穩定可靠地實現數據傳輸,滿足各種條件的需要。

2019-08-16 08:31:36

通信工程叢書--數據傳輸

這資料還是不錯的,可供參考學習哦!

2006-03-25 00:53:30 29

29 TDTC-3021是一款基于4G網絡全網通的無線數據終端產品,為遠方設備的監測、遠程抄表等應用提供數據傳輸通道。它采用支持中國移動、聯通、電信的4G全頻段的數據采集及傳輸。

該模塊可以

2021-09-09 11:33:08

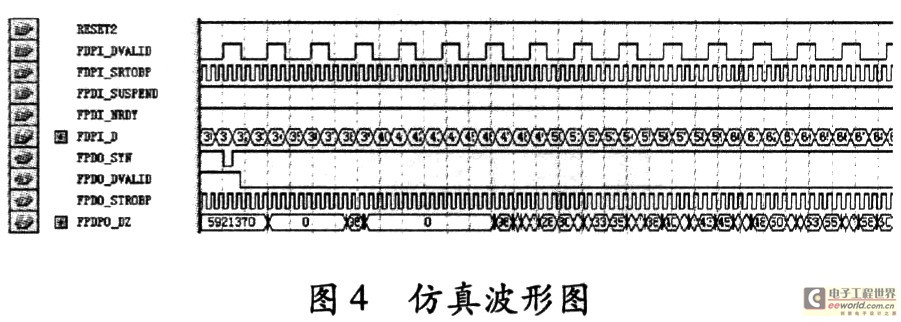

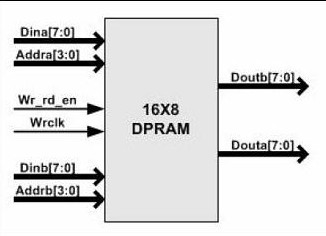

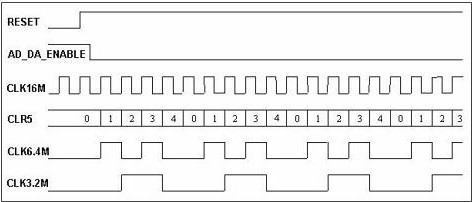

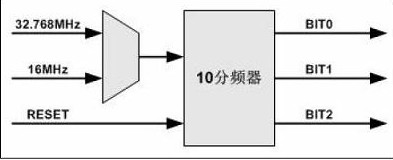

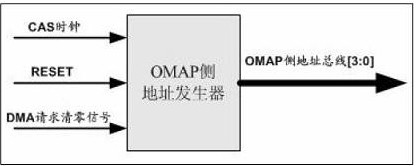

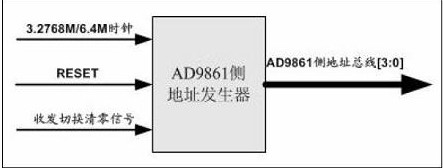

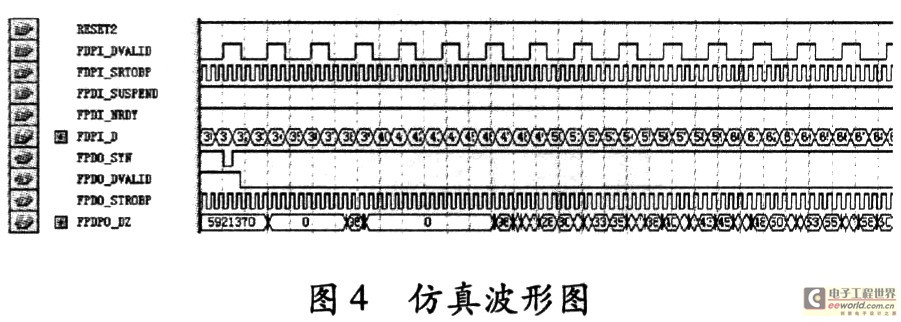

提出了一種利用CPLD有效解決通信數據傳輸問題的方案,詳細分析了CPLD在系統中的作用、工作原理和設計方法,并給出仿真以及實測結果,結果證實了此種方案的可行性和優越性。

2008-12-27 16:01:23 12

12 本文主要針對單片機在有線數據傳輸方面的應用,介紹了一種基于單片機MSP430 實現的MODEM 的數據傳輸系統。方案采用一個嵌入式的MODEM 作為系統傳輸數據的MODEM,MODEM 和單片機通

2009-06-13 13:38:28 20

20 2.5 數據傳輸介質 傳輸介質是通信網絡中連接計算機的具體物理設備和數據傳輸物理通路。傳輸介質的特性包括物理描述、傳輸特性、信號發送形式、

2009-06-27 21:47:04 0

0 為解決農電各個系統信息孤島的現象,利用消息中間件進行數據傳輸,確保數據準確、安全、可靠,實現農電聯網運營。分析了農電數據傳輸系統的需求,設計了數據傳輸軟件, 描

2009-08-18 10:32:08 10

10 本文通過一套數據采集卡的設計介紹了PCI 總線數據傳輸的基本過程,給出了系統整體設計方案和PCI 接口通信方式及驅動程序實現,并著重討論了PCI 數據傳輸中影響傳輸速率的

2009-09-21 10:19:54 34

34 數據傳輸PPT課件:傳輸介質本地異步通信遠距離通信雙絞線:由一對纏繞在一起的銅導線組成,纏繞在一起是為了減少干擾。雙絞線最早用于電話系統中,目前是桌面計

2009-11-24 09:34:18 0

0 基于PC 機的無線水文信息數據傳輸系統的設計與實現摘要:PC 機與無線數據傳輸模塊作為中心控制, 與ARM2132 單片機和nRF905 構成多個下位機進行無線數據通信, 將

2010-04-23 14:10:43 29

29 移動通信是當今通信領域最為活躍的分支之一,移動通信滿足了人類隨時隨地的個人通信要求,但是無線電信道中存在衰落、干擾等多種因素,使得數據傳輸性能差。因此,如

2010-10-11 16:53:17 21

21 ??? 在數字通信中的數據傳輸速率與調制速率是兩個容易混淆的概念。數據傳輸速率(又稱碼

2006-04-16 23:44:28 2511

2511

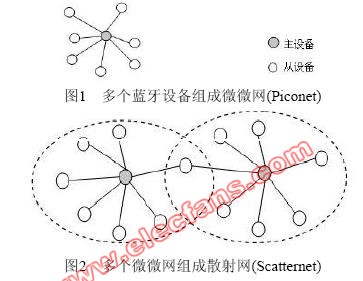

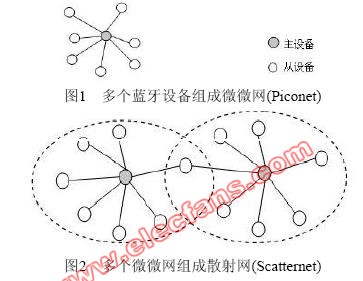

藍牙網絡數據傳輸分析

藍牙網絡的結構微微網是實現藍牙無線通信的最基本方式。每個微微網只有一個主設備,一個主設備

2008-12-16 01:17:35 2552

2552

什么是內部數據傳輸率

數據傳輸率的單位一般采用MB/s或Mbit/s,尤其在內部數據傳輸率上官方數據中更多的采

2009-06-17 07:39:29 1506

1506 基于FPDP的高速數據傳輸系統設計

隨著電子技術的高速發展,越來越多的信號處理系統,需要高速的數據采集和大吞吐量的數據傳輸,來實現數據的高速實時處理能力。

2009-12-01 09:41:44 2031

2031

SCSI硬盤數據傳輸率 數據傳輸率在實際使用中最重要的是指SCSI硬盤的內部數據傳輸率,也就是硬盤磁頭與

2009-12-17 14:31:22 786

786 IDE數據傳輸模式

隨著技術的發展,產品對數據傳輸速度要求的提高,IDE接口硬盤的數

2009-12-25 14:58:51 384

384 硬盤外部數據傳輸率 硬盤數據傳輸率的英文拼寫為Data Transfer

2009-12-25 15:21:49 381

381 Modem數據傳輸標準

數據傳輸標準是指MODEM的

2009-12-28 13:29:15 911

911 RAID卡的數據傳輸速度 數據傳輸速度是指硬盤接口的傳輸速度。比如ATA100接口硬盤的數據傳輸速度為100MB/S

2010-01-09 10:47:53 1898

1898 什么是U盤的數據傳輸率

便攜存儲是依靠USB接口與系統相連,其接口的速度就限制著移動硬盤的數據傳輸率。目前的US

2010-01-30 10:21:25 622

622 U盤的寫入數據傳輸率 U盤是依靠USB接口與系統相連,其接口的速度就限制著移動硬盤的數據傳輸率。目前的USB1.1接口能提供12Mbps;USB 2.0

2010-01-30 10:25:41 679

679 數據傳輸,數據傳輸的工作方式有哪些?

將數據從一個地方傳輸到另一個地方的方法多得令人難以置信。

數

2010-03-18 14:41:52 5946

5946 數據傳輸速率是什么意思

數據傳輸速率是通過信道每秒可傳輸的數字信息量的量度。數據傳輸速率也稱為吞吐率。數據傳輸速率由很

2010-03-18 14:45:20 4934

4934 什么是數據傳輸中的成幀

數據傳輸中的成幀

成幀技術是一種用來在一個比特流內分配或標記信道的技術,為電信提供選擇基本的時隙結構和管理方式、錯誤

2010-03-18 14:46:33 3654

3654 數字數據傳輸(DDN),數字數據傳輸(DDN)的工作原理是什么?

概述 計算機通信技術層出不窮,國民經濟的飛速發展,金融、證券、

2010-03-19 14:25:18 2414

2414 數據傳輸技術中的幾個術語

數據信息和數據通信、信道和帶寬、信道傳輸速率與通信方式、基帶傳輸、寬帶傳輸、 傳輸頻率與傳輸速率。

雙絞線

2010-11-06 08:44:08 1791

1791 在嵌入式數據傳輸系統中經常會遇到DSP芯片與模/數轉換器接口的問題,為提高信號的采樣、傳輸速度與精度,增強系統可靠性,給出了基于DSP芯片的多通道緩沖串口(McBSP)在數據傳輸

2011-05-03 18:05:53 34

34 利用嵌入式平臺的硬件、軟件技術、開發了基于GPRS網絡進行數據傳輸的嵌入式數據傳輸終端設備。通過設計一種應用層通信協議,很好地解決了在不可靠的無線傳輸鏈路上進行數據傳輸

2011-09-13 11:02:00 62

62 WNS是為傳感器實現無線網絡數據傳輸而設計的產品。該產品有嵌入式無線數據傳輸模塊和獨立部件可滿足各類傳感器配套選擇。

2017-09-25 17:20:04 13

13 在車載自組織VANETs中,為解決車輛間通信數據傳輸不流暢的問題。提出采用3G輔助VANETs的數據傳輸技術。在無法利用VANETs多跳通信傳輸數據時,啟動3G傳輸,將此方案命名為3G,首先建立

2017-11-08 09:51:54 4

4 針對當前各行業對無線數據傳輸的需求情況,設計了基于 M SP430F 12x[ 系列單片機與 C C llO0 無線數據傳輸芯片結合的無線數據傳輸模塊。

2018-04-20 16:02:20 8

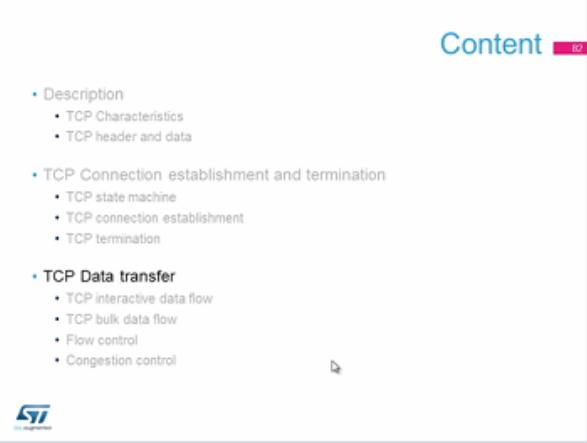

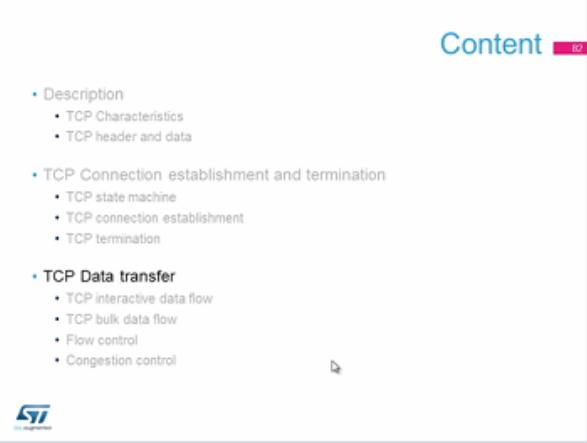

8 介紹了tcp協議:數據傳輸的問題(交互式數據傳輸,批量數據傳輸,流量控制,擁塞避免)

2018-07-03 11:05:00 3136

3136

ADI公司的iCoupler?數字隔離器使用芯片級微變壓器作為耦合元件,將數據傳輸通過高質量聚酰亞胺隔離柵。iCoupler隔離器中主要使用兩種數據傳輸方法:單端和差分。選擇數據傳輸機制時,需要進行工程設計取舍,以優化所需的終端產品特性。在單端數據傳輸中,我們使用變壓器,初級繞組的一端接地。

2019-01-01 10:51:00 9658

9658

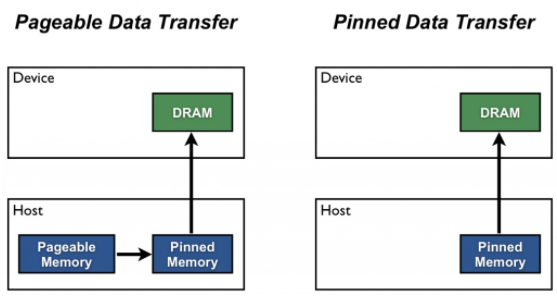

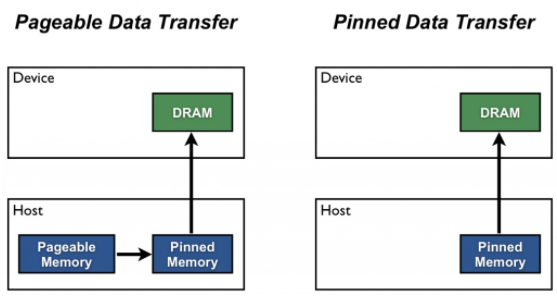

這篇文章的重點是提高數據傳輸的效率。在 下一篇文章 中,我們討論了如何將數據傳輸與計算和其他數據傳輸重疊。

2022-04-11 10:32:53 1891

1891

數據傳輸技術主要用于多機通信領域,一般在數據交換過程中,為保證數據的穩定可靠傳輸而制定的特殊傳送規則。其傳輸過程也根據傳輸的物理介質而不同。

2023-02-22 11:14:25 1021

1021 數據傳輸方式是數據在信道上傳送所采取的方式。若按數據傳輸的順序可以分為并行傳輸和串行傳輸;若按數據傳輸的同步方式可分為同步傳輸和異步傳輸;若按數據傳輸的流向和時間關系可以分為單工、半雙工和全雙工數據傳輸。下面跟著科蘭布線小編一起詳細來了解一下吧。

2023-03-24 11:04:16 1109

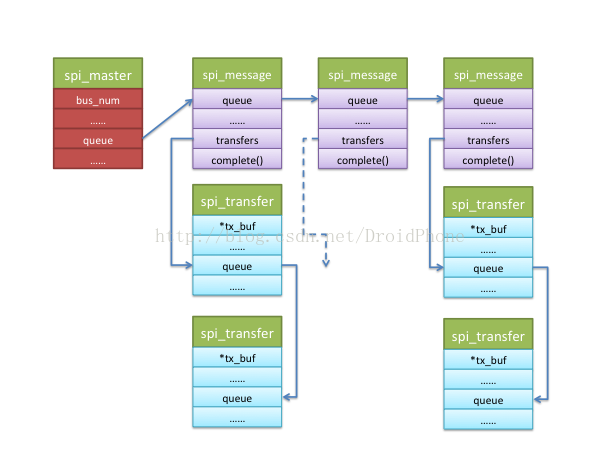

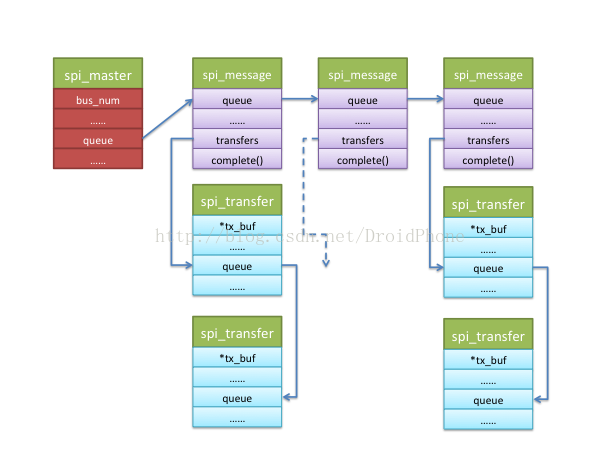

1109 SPI 數據傳輸可以有兩種方式:同步方式和異步方式。 同步方式:數據傳輸的發起者必須等待本次傳輸的結束,期間不能做其它事情,用代碼來解釋就是,調用傳輸的函數后,直到數據傳輸完成,函數才會返回。 異步

2023-07-25 10:54:22 2899

2899

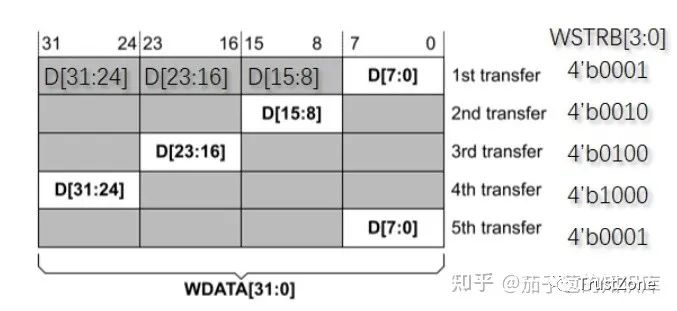

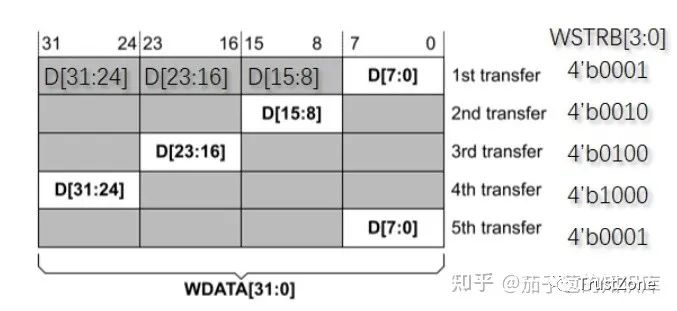

在 AXI 數據傳輸過程中,主要涉及到 ?窄位寬數據傳輸(Narrow Transfer) ?非對齊傳輸(Unaligned Transfer) ?混合大小端傳輸(mix-endianness

2023-10-31 16:17:12 505

505

在現代通信技術中,半雙工和全雙工數據傳輸是兩種常見的數據傳輸方式。本文將為大家詳細解析這兩種傳輸方式在芯片設計中的應用和區別,幫助大家更好地理解芯片設計中的通信原理。

2023-11-19 11:31:44 342

342

電子發燒友App

電子發燒友App

評論