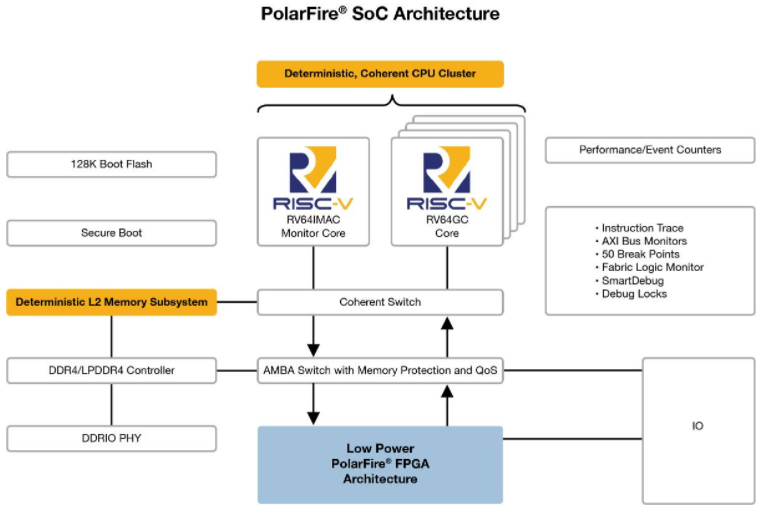

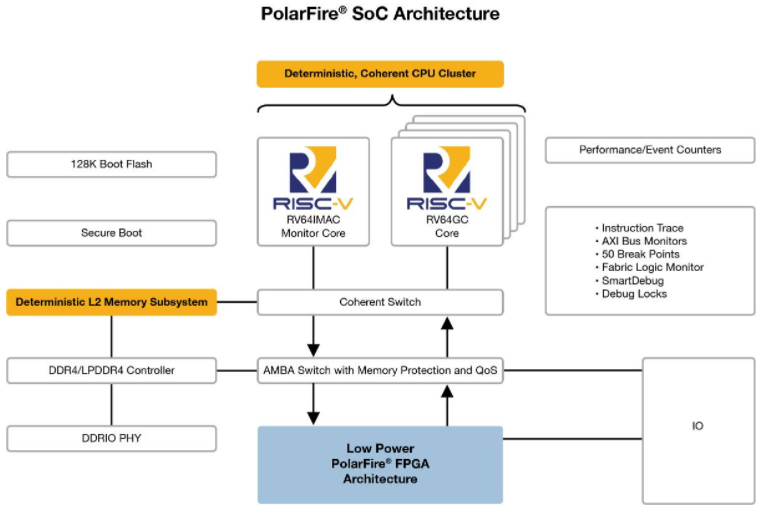

Microchip Technology Inc.(美國微芯科技公司)啟動了PolarFire?片上系統(SoC)現場可編程門陣列(FPGA)早期使用計劃(EAP)。

2019-12-11 16:55:15 1157

1157 的Zynq 7000, 找了一個HLS的教程,就開始了如下入門實驗,體驗高級語言綜合設計IP。Vivado HLS是Xilinx 推出的高層次綜合工具,采用C/C++語言進行FPGA設計。HLS提供了一些

2020-10-14 15:17:19 2880

2880

Microchip 今日推出經優化的耐輻射RT PolarFire FPGA,為新興的高性能太空應用市場帶來具備上述功能的新產品。

2019-10-23 17:04:10 822

822 Microsemi PolarFire FPGA視頻和成像套件配備帶有板載PolarFire FPGA的PolarFire視頻與成像板以及一個雙攝像頭傳感器板。

2019-11-08 11:23:33 923

923 Microchip開發系統高級總監Rodger Richey表示:“目前,許多MCU產品的功能安全工具成本非常高,Microchip推出的功能安全產品的價格僅為某些競爭性解決方案的三分之一,而且提供卓越的全球技術支持,助力客戶加快產品上市并進一步簡化開發流程。”

2020-01-21 00:27:00 3986

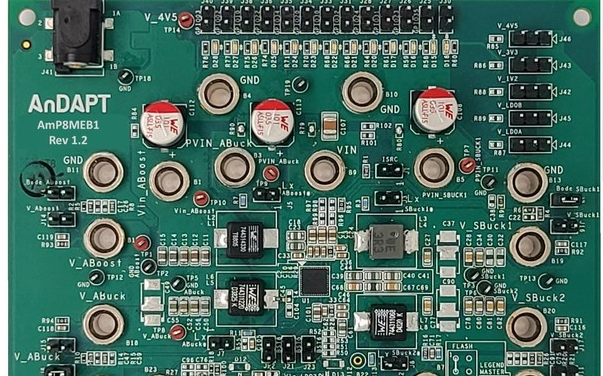

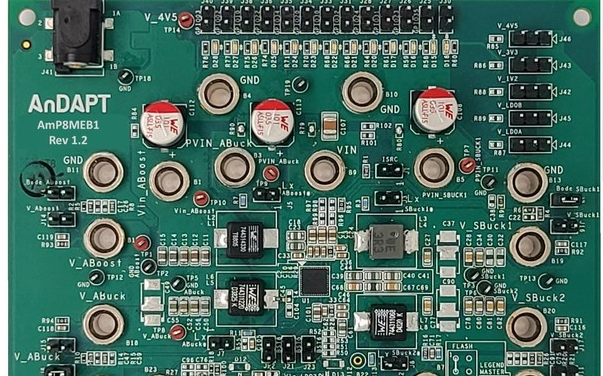

3986 AnDAPT現在支持使用集成、靈活和可編程的AmP電源管理IC為Microchip PolarFire FPGA供電。

2022-01-19 10:46:27 2192

2192

? 合集關鍵字 :Mi-V峰會;Microchip;Polarfire SOC FPGA;Mercury+ MP1; RISC-V 今年, Enclustra 發布了其首款基于 Microchip

2022-08-15 15:20:25 641

641

linux中高級開發工程師1. 精通linux環境c/c++應用編程,熟練makefile編寫。2. 精通常用的數據結構算法,hash表、紅黑樹、自動機等。3. 精通linux下進程間通信、多線程開發、網絡

2014-01-03 13:11:21

,一般將硬件初始化的工作交給匯編,比較復雜的操作交給C語言。③C語言具有很高的運行效率。2.嵌入式開發中的地位——開發工具3.高級語言中的低級語言:面向過程VS面向對象雙系統C/C++ 工程師更稀缺C

2021-11-25 10:47:33

GPU 讀取一款用 C++ 編寫的軟件一樣。就是這么簡單。

但為了優化該編程過程,您需要訪問正確的平臺。幸運的是,AMD 擁有完美的解決方案,這是一套開創性的工具,可在 FPGA 編程過程的每個環節為

2023-06-28 18:18:57

的高級語言(如C++和C++)的準入,這一點讓眾多軟件工程師甘之如飴。與硬件描述語言(如VHDL和VerilogHDL)不同,它并不是由一小部分工程師掌握的工具。當然,它也有局限性:語言限制,就像非可合成

2021-07-10 08:00:00

`為客戶提供完美的硅芯片解決方案是MICROCHIP堅持不懈的目標。但我們不只局限于提供硅芯片,還需要編程器、編譯器、參考設計、函數庫、應用筆記和評估板等支持工具,以助您最高效地完成評估和產品開發

2011-03-09 14:59:00

的設計工具和資源,以幫助開發人員采用和改進 RISC-V 應用程序設計。這些工具可與各種硬件套件結合使用——用于 PolarFire FPGA 的 PolarFire 評估套件和Icicle 套件

2021-09-07 17:59:56

、基于 RISC-V 的 PolarFire? SoC FPGA 打造,匯集了眾多的 Mi-V 合作伙伴,助力加速不同行業的客戶設計部署和商業應用。 設計人員現在可以開始開發和評估實時操作系統(RTOS

2020-09-25 11:39:42

Microchip提供了一系列高度集成的開發工具,可以簡化應用程序的開發過程。這些工具分為核心開發工具和附屬工具。基本開發工具主要有:•MPLAB®集成開發環境

2011-03-08 16:50:21

目前有一個算法庫 用的c++ ?用ccs在dsp上可以調試

現在希望把庫放在8168的dsp上 ?需要將c++轉換成c 有個工具

mmCC C++-to-C Translator、

不知道論壇里有沒有 或者大家誰有

如果找不到mmcc

那么 ?8168上dsp用c調用c++庫 有沒有可行性

2018-06-21 13:14:22

開發c++應用程序。

這本書只涵蓋了ARMC+t特有的信息。它旨在與ARM軟件開發工具包2.11版本文檔套件一起使用。

2023-08-08 06:29:26

模擬過程完成沒有0錯誤,但在合成期間顯示錯誤。我無法找到錯誤。我在合成期間在HLS工具中收到這樣的錯誤“在E中包含的文件:/thaus / fact_L / facoriall

2020-05-21 13:58:09

、自然語言處理等核心算法,可助力開發者快速實現順暢自然的智能語音交互體驗。提供全棧式軟硬件開發,兼容更多開發場景,支持用戶自定義設 計,幫助開始者快速實現產品開發,打造專屬 AI 語音產品。`

2020-06-28 17:55:59

TI CC2541開發套件

2023-03-25 01:27:25

`CPLD/FPGA高級應用開發指南第1章可編程邏輯器件與EDA技術第2章Xilinx CPLD系列產品第3章Xilinx FPGA系列產品第4章Xilinx ISE應用基礎第5章FPGA高級

2013-06-02 10:13:17

這個名的本意是希望他成為C++編程語言的高效軟件開發平臺。然而,將Chromium裁剪成HiSDP并使之適合用于集團服務器環境下的軟件開發還是經歷了一些波折。最大的問題在于,Chromium的開發環境

2018-06-19 16:32:58

HiHope 滿天星智能家居開發套件

2023-03-28 13:07:10

潤和滿天星系列Pegasus智能小車開發套件,基于海思Hi3861V100芯片,支持OpenHarmony輕量系統,實現巡線、避障功能通過尋跡模塊獲取路面軌道數據,運用尋跡算法使得智能小車可以按照固定軌道運行

2023-03-28 13:07:10

外設傳感器,套件可通過積木組合的形式,實現多種應用場景,套件重點圍繞智能回收站,有回收站定位人體紅外、自動開蓋、傾倒檢測、滿載上報功能等。套件配置OpenOCD JTAG調試工具方便開發者快速調試。

2023-03-28 13:07:10

意法半導體(ST)旗下全資子公司Portland Group公布該公司的Fortran、C和C++編譯器及開發工具套件7.1版全面上市。PGI編譯器和開發工具被廣泛用于高性能計算技術(HPC),即以復雜現象的建模和仿真為主的科研計算領域,如海洋建模、天氣預報、地震分析、生物信息分析技術等。

2019-07-17 07:18:38

加利福尼亞州,圣何塞— 2014年9月3日– S2C公司今日宣布TAI Player Pro 5.1版本正式發布。此次最新版本將幫助用戶加速FPGA原型開發、提高工程師的生產力,以及實現最高的原型

2019-07-02 06:23:44

機器人設計及智能項目開發資料設計教程JAVA開發視頻教程\培訓視頻教程C# .net開發視頻教程\培訓視頻教程C++開發視頻教程\培訓視頻教程匯集海量文檔資料,技術開發資料,項目設計資料,硬件原理圖PCB,軟件源碼包、開發工具包、開發設計技術文檔等

2009-12-10 15:48:43

/C++的編程技巧者優先, 對圖像信號處理、識別、編解碼等算法有較好的基礎;4、有良好的英文閱讀能力; 5、具有良好的團隊合作精神和刻苦鉆研精神,責任心強,能承受一定的工作壓力;6、有智能交通行業產品DSP開發經驗者優先。工作地點:武漢有意向者請窗我:QQ:1940783351

2013-07-16 11:07:23

的高級語言(如C++和C++)的準入,這一點讓眾多軟件工程師甘之如飴。與硬件描述語言(如VHDL和VerilogHDL)不同,它并不是由一小部分工程師掌握的工具。當然,它也有局限性:語言限制,就像非可合成

2021-07-06 08:00:00

者可以使用 C/C++ 語言來編寫 FPGA 邏輯代碼,而不需要了解寄存器傳輸級 (RTL) 語言或 FPGA 架構。

HLS可以提高開發效率和降低開發難度,因為 C/C++ 語言比 RTL 語言更高級

2023-10-13 20:11:51

/C++進行設計,然后由Vivado HLS編譯器將C代碼綜合成HDL描述,最后再進行邏輯綜合得到網表,這個網表最終會被映射到具體的FPGA器件上。就像C語言或者其他高級語言針對不同的處理器架構有著

2020-10-10 16:44:42

設計的綜合。Vivado High Level Synthesis(即HLS,高層次綜合)工具使用C、C++或System C語言在更抽象的算法層次描述設計,并將C代碼綜合成RTL級的HDL描述

2020-10-10 16:48:25

ap_none接口的IP核。在本章我們將通過呼吸燈實驗,來學習如何使用Vivado HLS工具生成一個帶有AXI4-Lite總線接口的IP核,并學習Vivado HLS工具C/RTL協同仿真平臺的使用,以及在

2020-10-10 17:01:29

拼接算法試用計劃:申請理由本人從事圖像處理,圖像編碼算法有十年開發經驗,熟悉xilinx FPGA的編程,曾設計過ISP算法,由于有監控場景需要寬幅圖像,想借助發燒友論壇和米爾MYD-C7Z020平臺

2019-10-30 17:03:31

庫文件,甚至可以引進HDL程序,并進行仿真,最終生成網表文件,放到FPGA中執行。軟件算法工程師不需要特別的培訓,利用他們熟悉的C語言就可以直接進行硬件開發,減輕了硬件開發的瓶頸和壓力。隨著算法描述

2015-01-13 16:34:40

,我們一直在使用Vivado給我們提供的IP或者使用硬件描述語言制作 IP 。今天我們將講解如何使用HLS-高級綜合語言來創建屬于我們自己的IP。我們將使用的工具稱為Vitis HLS,此后稱為 HLS

2022-09-09 16:45:27

將C、C++等語言轉化成硬件描述語言,同時支持基于OpenCL等框架對Xilinx可編程邏輯器件進行開發,可加速算法開發的進程,縮短產品上市時間。HLS基本開發流程如下:(1) HLS工程新建/工程

2021-02-19 18:36:48

編寫C或C++應用程序時,需要使用編譯器工具鏈將其編譯為機器代碼。然后,您可以在基于Arm的處理器上運行此編譯的可執行代碼,或者使用模型對其進行模擬。

裸機編譯編譯器工具鏈包括以下組件:

?將C

2023-08-02 17:28:39

學習方向:嵌入式+人工智能嵌入式是一門技術學習目標1.嵌入式開發概述;(面向對象在嵌入式開發中角色)2.嵌入式Linux C++編程;(C++概述、C++學習方法、C++開發工具)3.C到C++升級

2021-12-24 07:32:38

。

Xilinx Vivado HLS (High-Level Synthesis,高層次綜合) 工具支持將 C 、C++等語言轉化成硬件描述語言,同時支持基于 OpenCL 等框架對 Xilinx

2023-08-24 14:40:42

。Xilinx Vivado HLS (High-Level Synthesis,高層次綜合) 工具支持將 C 、C++等語言轉化成硬件描述語言,同時支持基于 OpenCL 等框架對 Xilinx

2023-01-01 23:52:54

(High-Level Synthesis,高層次綜合) 工具支持將 C 、C++等語言轉化成硬件描述語言,同時支持基于 OpenCL 等框架對 Xilinx 可編程邏輯器件進行開發,可加速算法開發的進程,縮短

2023-01-01 23:46:20

(High-Level Synthesis,高層次綜合) 工具支持將 C 、C++等語言轉化成硬件描述語言,同時支持基于 OpenCL 等框架對 Xilinx 可編程邏輯器件進行開發,可加速算法開發的進程,縮短

2023-08-24 14:54:01

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高層次綜合)工具支持將C、C++等語言轉化成硬件描述語言,同時支持基于OpenCL等框架

2021-11-11 09:38:32

::Blocks是一個開源的、跨平臺的集成開發環境(IDE),支持C/C++等語言的開發,并且可以配合各種插件進行嵌入式開發。 7、PlatformIO:這是一款基于Python的開源工具,可以用來構建和調試嵌入式

2023-11-10 11:03:04

在《算法電路的合成:FPGA,ASIC和嵌入式系統》中,作者采用了一種新穎的方法來呈現用于合成算法電路的方法和示例,以更好地反映當今計算機系統設計者和工程師的需要。不像其他出版物,將討論限制

2018-12-20 16:14:53

和生成比特流以對FPGA進行編程4 - 將比特流導入并阻塞到SDK中,基于此生成板級支持包(BSP)并與Zedboard連接。順便說一下,SDK的目標是成為我在Vivado HLS中的測試平臺嗎?即在計算機中觀察Zedboard產生的結果是否為例外情況。

2020-03-24 08:37:03

)是一個由自服務API、工具、文件和實例代碼的集合,可輕松構建你自定義的Alexa skills,然后發布。機智云開源套件 Gokit 是一塊標準的量產級嵌入式開發板,即代表了通用型智能設備。硬件集成

2017-03-31 11:54:05

。Vivado HLS作為該套件的一個組件,能幫助設計人員將采用C/C++語言開發的算法編譯為RTL,以便在FPGA邏輯中運行。Vivado HLS工具非常適用于嵌入式視覺設計。在此流程中,您用C/C++

2014-04-21 15:49:33

你好,我有一個與switch語句的合成有關的問題。我開始使用Vivado HLS并且我已經創建了一個小的file.cpp,僅用于學習,但是當Vivado HLS合成文件時,我沒有得到任何開關語句

2019-11-05 08:21:53

您好,我目前正在嘗試使用Vivado HLS在FPGA上合成加密算法。我根據需要拆分了C ++代碼并包含了一個測試平臺,但是當我嘗試模擬代碼時,我得到一個錯誤,說找不到測試平臺。我附上了錯誤圖片和項目檔案,希望有人能幫我找到解決方案。謝謝!LBlock_fpga.zip 48 KB

2020-05-15 09:26:33

進行編譯的。本文僅驗證了采用高級語言開發FPGA的可行性,還有很多優化工作待完善,僅以此文為大家提供一個新的視角,為軟件開發人員利用FPGA進行算法加速做前期調研,歡迎感興趣的同事共同交流。

2017-09-25 10:06:29

,10.1寸多觸摸顯示屏等整體硬件,一站式解決了開發者對硬件平臺的選擇與適配的問題。HarmonyOS2.0發布后,Firefly會繼續深入HarmonyOS的生態。除了“HarmonyOS開發套件”,Firefly還推出了全國產化核心板系列,全面支持國內芯片與科技產業的發展,為客戶持續創造價值。`

2021-06-03 13:59:55

的問題。 鴻蒙2.0發布后,Firefly會繼續深入鴻蒙OS的生態。除了“鴻蒙開發套件”,Firefly還推出了全國產化核心板系列,全面支持國內芯片與科技產業的發展,為客戶持續創造價值。

2021-06-03 14:47:15

,10.1寸多觸摸顯示屏等整體硬件,一站式解決了開發者對硬件平臺的選擇與適配的問題。HarmonyOS2.0發布后,Firefly會繼續深入HarmonyOS的生態。除了“HarmonyOS開發套件”,Firefly還推出了全國產化核心板系列,全面支持國內芯片與科技產業的發展,為客戶持續創造價值。`

2021-06-07 11:10:54

客戶能夠在小至 11 × 11 毫米的封裝尺寸上實施解決方案。Microchip 的 PolarFire SoC FPGA Icicle 工具包非常適合智能嵌入式成像、物聯網、工業自動化、國防、汽車

2021-03-09 19:48:43

Intel Agilex? F系列FPGA開發套件Intel Agilex? F系列FPGA開發套件設計用于使用兼容PCI-SIG的開發板開發和測試PCIe 4.0設計。該開發套件還可通過硬核處理器

2024-02-27 11:51:58

MIDI合成算法及其FPGA實現.

2012-04-16 13:57:38 44

44 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進行 FPGA 設計的簡介

2016-01-06 11:32:55 65

65 FPGA學習資料教程之Xilinx-FPGA高級開發工具,感興趣的可以看看。

2016-09-01 15:27:27 0

0 HLS工具 以個人的理解,xilinx將HLS(高層次綜合)定位于更方便的將復雜算法轉化為硬件語言,通過添加某些配置條件HLS工具可以把可并行化的C/C++的代碼轉化為vhdl或verilog,相比于純人工使用vhdl實現圖像算法,該工具綜合出的代碼的硬件資源占用可能較多。

2019-10-12 17:34:00 1961

1961

高層次綜合(High Level Synthesis, HLS)是Xilinx公司推出的最新一代的FPGA設計工具,它能讓用戶通過編寫C/C++等高級語言代碼實現RTL級的硬件功能。隨著這款工具

2018-07-14 06:42:00 5868

5868 測試用的大量采樣數據,完成對硬件系統原型的評估。對于I/Q壓縮算法等類似高數據吞吐量的應用,采用Vivado HLS工具進行測試評估更加的方便。

2017-11-17 02:25:41 1267

1267

使用Xilinx Vivado HLS(Vivado 高層次綜合)工具實現浮點復數QRD矩陣分解并提升開發效率。使用VivadoHLS可以快速、高效地基于FPGA實現各種矩陣分解算法,降低開發

2017-11-17 17:47:43 3293

3293

如果您正在努力開發計算內核,而且采用常規內存訪問模式,并且循環迭代間的并行性比較容易提取,這時,Vivado? 設計套件高層次綜合(HLS) 工具是創建高性能加速器的極好資源。通過向C 語言高級算法描述中添加一些編譯指示,就可以在賽靈思FPGA 上快速實現高吞吐量的處理引擎。

2017-11-17 18:12:01 1647

1647 、邊緣模糊等級和脈沖噪聲等指標評估基于該算法圖像處理效果。與傳統時域算法作對比,對比結果表明該算法在處理效果和運算速度上的優異性。基于Zedboard開發板,運用Vivado HLS高級綜合工具將算法的C程序綜合成硬件IP,并搭建了包含ARM處理器和VGA等

2017-12-12 14:07:38 2

2 本文介紹了PolarFire FPGA主要特性,低功耗特性,可靠特性和安全特性,框圖,以及PolarFire FPGA評估板硬件特性,框圖,電路圖和元件表以及PCB元件布局圖。

2018-06-17 18:06:00 5573

5573

HLS,高層綜合)。這個工具直接使用C、C++或SystemC 開發的高層描述來綜合數字硬件,這樣就不再需要人工做出用于硬件的設計,像是VHDL 或Verilog 這樣的文件,而是由HLS 工具來做這個事情。

2018-06-04 01:43:00 7171

7171

高級綜合( HLS)工具及其入門指南

2018-06-20 00:08:00 3952

3952

賽靈思公司推出 Vivado 設計套件 HLx 版本,為All Programmable SoC 和 FPGA以及打造可復用的平臺提供了全新超高生產力設計方法。新版 HLx 包括 HL 系統版本

2018-08-17 11:43:00 2677

2677 美高森美公司(Microsemi ) 宣布提供低成本IGLOO 2 FPGA評測工具套件,為客戶提供PCI Express (PCIe)兼容外形尺寸評測平臺。這款功能齊全的工具套件可讓設計人員快速評測美高森美最近發布的IGLOO2 FPGA器件的集成度、低成本、安全性、即時性和高可靠性特性。

2018-09-18 16:49:00 1399

1399 關鍵詞:Actel , Fusion , 高級 , 工具 , 套件 愛特 (Actel) 正式付運Fusion高級開發工具套件,協助設計人員開發系統和功率管理應用。該工具套件帶有Actel

2018-10-24 20:44:01 560

560 使用Spartan-6 FPGA消費類視頻套件加速DTV設計中高級視頻算法的開發。

與消費者部門主管Harry Raftopoulos近距離觀看套件。

2018-11-28 06:15:00 1714

1714 Xilinx 戰略應用高級工程師。專注于 C/C++ 高層次綜合,擁有多年利用 Xilinx FPGA 實現數字信號處理算法的經驗,對 Xilinx FPGA 的架構、開發工具和設計理念有深入的理解。

2019-08-01 15:30:49 1869

1869 接著開始正文。據觀察,HLS的發展呈現愈演愈烈的趨勢,隨著Xilinx Vivado HLS的推出,intel也快馬加鞭的推出了其HLS工具。HLS可以在一定程度上降低FPGA的入門門檻(不用編寫

2019-07-31 09:45:17 6232

6232

Microchip啟動了PolarFire片上系統(SoC)現場可編程門陣列(FPGA)早期使用計劃(EAP)。

2019-12-16 15:16:21 631

631 Microchip啟動了PolarFire片上系統(SoC)現場可編程門陣列(FPGA)早期使用計劃(EAP)。

2019-12-26 15:39:03 1100

1100 ,Microchip Technology Inc.(美國微芯科技公司)宣布推出業界首款基于 RISC-V 的SoC FPGA開發工具包。這款名為Icicle 的開發工具包專為業界領先的低功耗、低成本

2020-09-24 09:37:29 3047

3047 基于RISC-V的SoC FPGA屬于Microchip RISC-V生態系統,這是支持各種操作系統和生態系統合作伙伴的工具套件和設計資源組合。

2021-02-05 14:23:46 2222

2222 算法都是由開發人員使用C++語言原生開發的,而他們對底層FPGA硬件知之甚少或一無所知。為了支持這一重要的開發群體,Microchip Technology Inc.(美國微芯科技公司)推出了名為SmartHLS的HLS設計工作流程,成為其PolarFire FPGA系列產品的新成員。

2021-09-07 11:50:27 6446

6446 Vitis HLS 是一種高層次綜合工具,支持將 C、C++ 和 OpenCL 函數硬連線到器件邏輯互連結構和 RAM/DSP 塊上。Vitis HLS 可在Vitis 應用加速開發流程中實現硬件

2022-05-25 09:43:36 1930

1930 由于它是一個開放標準,為 PolarFire 設備開發的代碼可以擴展和縮減 Microchip FPGA SoC 產品組合以及其他 RISC-V RV64GC 目標,而無需從頭開始。

2022-06-01 10:18:56 1217

1217

在整個流程中,用戶先創建一個設計 C、C++ 或 SystemC 源代碼,以及一個C的測試平臺。通過 Vivado HLS Synthesis 運行設計,生成 RTL 設計,代碼可以是 Verilog,也可以是 VHDL。

2022-06-02 09:48:17 6129

6129 出于這個原因,Microchip 繼續在其 PolarFire FPGA SoC 系列中進行創新——推出的具有 25K 邏輯元件和硬化四核 RISC-V CPU 的 MPFS025 SoC。

2022-07-10 15:42:15 907

907

HLS的FPGA開發方法是只抽象出可以在C/C++環境中輕松表達的應用部分。通過使用Vivado(Xilinx)或Intel(Quartus)工具,HLS工具流程基本上可用于任何BittWare板。

2022-08-02 09:18:32 1340

1340

1、HLS簡介 HLS(High-Level Synthesis)高層綜合,就是將 C/C++的功能用 RTL 來實現,將 FPGA 的組件在一個軟件環境中來開發,這個模塊的功能驗證在軟件環境

2022-12-02 12:30:02 2570

2570 推理解決方案的快速開發平臺 》的在線研討會。 VectorBlox平臺是一款軟件開發工具包(SDK),可實現基于PolarFire FPGA的機器學習(ML)推理。這款SDK有多種工具,無需對FPGA

2022-12-12 20:25:08 605

605 HLS ?(high-level synthesis)稱為高級綜合, 它的主要功能是用 C/C++為 FPGA開發 算法。這將提升FPGA 算法開發的生產力。 ?? Xilinx 最新的HLS

2023-01-15 12:10:04 2968

2968 AMD Vitis HLS 工具允許用戶通過將 C/C++ 函數綜合成 RTL,輕松創建復雜的 FPGA 算法。Vitis HLS 工具與 Vivado Design Suite(用于綜合、布置和布線)及 Vitis 統一軟件平臺(用于所有異構系統設計和應用)高度集成。

2023-04-23 10:41:01 652

652

。 ? 這些新工具進一步擴大了Microchip FPGA全面的工具和服務工具包,支持成熟的PolarFire系列器

2023-06-08 08:05:02 403

403 。 這些新工具進一步擴大了Microchip FPGA全面的工具和服務工具包,支持成熟的PolarFire系列器件

2023-06-15 09:05:01 311

311 該項目包含使用高級綜合 (HLS) 的 2D 中值濾波器算法的實現。該項目的目標是在不到 3 ms的時間內對測試圖像進行去噪,同時消耗不到 25% 的可用 PL 資源。特征如下:

2023-07-03 09:06:43 466

466

安全當前已成為各垂直市場所有設計的當務之急。今天,有進一步證據向系統架構師和設計人員證明,使用Microchip Technology Inc.(美國微芯科技公司)的PolarFire FPGA

2023-09-05 11:50:01 291

291 安全當前已成為各垂直市場所有設計的當務之急。今天,有進一步證據向系統架構師和設計人員證明,使用Microchip Technology Inc.(美國微芯科技公司)的PolarFire? FPGA

2023-09-05 11:49:53 905

905 Microchip推出針對智能邊緣設計的定制PolarFire FPGA和SoC解決方案堆棧,以加快開發速度,同時推動FPGA的采用。 為了加快智能邊緣設計,Microchip Technology

2023-10-26 18:09:50 746

746

電子發燒友App

電子發燒友App

評論