一、TDC計時技術

時間數字轉換(Time-to-Digital Converter,TDC)是一種用來測量時間的電路,它將連續的時間信號轉換為數字信號,從而實現時間測量的數字化。精密時間間隔測量技術、測量精度通常為亞納秒級,廣泛應用于激光測距、成像、衛星導航、高能物理實驗以及醫學成像等領域。

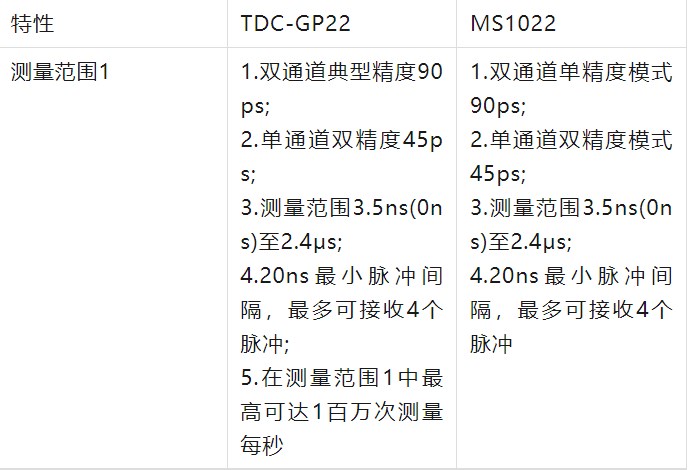

常用的TDC計時方法可以在專用集成電路(Application Specific Integrated Circuit,ASIC)中實現,比如德國ACAM公司推出的TDC-GPX系列,同時國內瑞盟科技也推出以其性能一樣的TDC測量芯片MS1022。表1比較了TDC-GP22和MS1022的測量范圍特性,可以看出基本一樣,因此此兩款芯片在低成本測量領域有著廣泛的運用。

表1 TDC-GP22和MS1022特性

常見的基于FPGA開發TDC計時技術有直接計數法,多相位時鐘采樣法,抽頭延遲線法等等。在本次講解中,主要講解基于多相位的時間數字轉換技術,后期也會推出多種基于抽頭延遲線法的開發例子。

采用多相位時鐘采樣法(MPCS),通過多相位時鐘插值,雖然無法達到基于抽頭延遲線法那種結構的皮秒級高精度,但也能設計出156ps左右的分辨率。這種實現方法更為穩定、資源占用更少,測量范圍更大,適用于對精度要求不是特別高的測距、成像系統中。

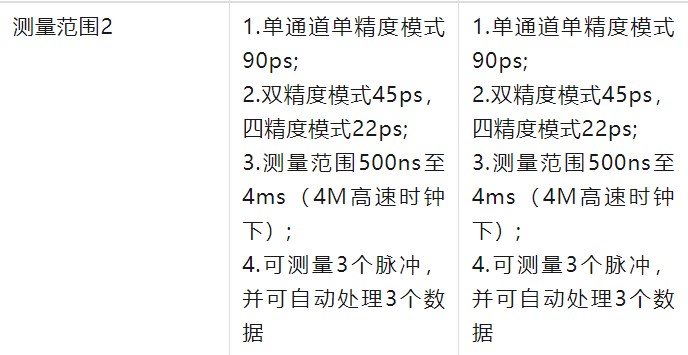

圖1為多相位時鐘采樣結構示意圖,其基本工作原理是把單個參考時鐘的直接計數法轉化為采用多路固定相移時鐘對時間間隔進行量化測量。

圖1 多相位時鐘采樣結構示意圖

圖2為基于8相位時鐘采樣示意圖,時鐘信號經過數字移相后輸出8路頻率相同,相位依次相差(這里n=8)的多路時鐘信號,等效于將每一個Clock周期時鐘n(這里n=8)次切片量化。

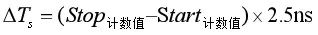

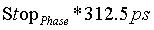

當選擇的n值越大,即對每個Clock時鐘周期劃分的越精細,分辨率越高,在這里相當于將Clock頻率提高了8倍。假設系統主時鐘為400Mhz(2.5ns),其測量分辨率變為2.5ns/8=312.5ps。其計算公式如式1所示。

圖2 基于8相位TDC計時設計

圖2 基于8相位TDC計時設計

(1)

(1)

其中, ,

, 為Start信號與時鐘Clk_0上升沿之間時間差=

為Start信號與時鐘Clk_0上升沿之間時間差= ,

, 為Start信號與時鐘Clk_0上升沿之間時間差=

為Start信號與時鐘Clk_0上升沿之間時間差= 。

。

圖3為8相位時鐘采樣時序等效圖,可以計算出Start和Stop的相位差。在輸入信號上升沿來之前輸出都為“0”,但在相移時鐘在到之間輸入信號由“0”~“1”電平跳變,對應相移時鐘采樣輸出為高電平“1”。

輸出寄存器組每8位一組,可以看出依次為:00000000,00000111,11111111,只要找到“0”~“1”電平跳變點即可得到當前輸入信號上升沿與最臨近的Clock上升沿的時間間隔,就能計算Start和Stop信號的相位差,從而根據公式1算出時間差。

圖3 8相位時鐘采樣時序等效原理圖

在時間間隔測量過程中,外部異步輸入時間間隔信號與板載基準時鐘信號存在著不同時鐘域問題,即存在亞穩態現象。在只有一路時鐘信號對其進行測量時,待測時間間隔信號需要利用計數時鐘信號進行同步處理。

而采用MPCS的TDC電路,待測時間間隔信號被多路相位時鐘信號量化,不需要考慮輸入信號與時鐘之間的相位位置,多相位時鐘存在一定的相位約束關系,其相位差值恒定不變,通過循環相移時鐘即可精確量化輸入時間間隔信號,但亞穩態產生概率更高,不可忽視。

電子發燒友App

電子發燒友App

評論