本人在北京工作6年以上,從事FPGA外圍接口設(shè)計(jì),非常熟悉PCI Express協(xié)議,設(shè)計(jì)調(diào)試了多個(gè)基于PCI Express接口的數(shù)據(jù)采集卡.本人非常熟悉Spartan-6, Virtex-5

2014-08-23 13:15:30

基于PCI Express的數(shù)據(jù)采集卡PCIe數(shù)據(jù)采集卡PCI Express數(shù)據(jù)采集卡本人在北京工作6年以上,從事FPGA外圍接口設(shè)計(jì),非常熟悉PCI Express協(xié)議,設(shè)計(jì)調(diào)試了多個(gè)基于PCI

2015-06-21 13:38:12

所阻塞,也一樣能進(jìn)行數(shù)據(jù)傳輸。盡管 PCI 總線在某些方面已有些過時(shí),但是轉(zhuǎn)變到PCI Express 還要經(jīng)過一個(gè)長(zhǎng)期過程,并且未來許多年里PCI 總線將仍然是I/O 擴(kuò)展的強(qiáng)有力競(jìng)爭(zhēng)者。隨著PCI

2019-05-10 07:00:07

Express 在客戶產(chǎn)品中固有的優(yōu)勢(shì)。為了能在今天創(chuàng)建解決明日問題的解決方案,并跟上時(shí)代迅速發(fā)展的步伐,Xilinx 公司在其 VirtexTM-5 LXT 器件中融入了硬 PCI Express 端點(diǎn)模塊

2019-05-08 07:00:47

,可以提供高達(dá)132MB/s的數(shù)據(jù)傳送速率;它具有嚴(yán)格的規(guī)范,只要符合PCI規(guī)范的擴(kuò)展卡插入任何PCI系統(tǒng)就能可靠地工作。但由于PCI總線協(xié)議的復(fù)雜性,其接口的實(shí)現(xiàn)比VESA、ISA和MCA等總線要困難

2018-12-17 11:23:00

PCI9050送到CPU。6、結(jié)束語由于PCI總線數(shù)據(jù)吞吐量大,傳輸速率高,所以現(xiàn)在PCI總線已經(jīng)慢慢取代了ISA總線成為主流。當(dāng)然,PCI總線協(xié)議要復(fù)雜的多,接口設(shè)計(jì)難度也就增大了。目前,設(shè)計(jì)PCI接口有

2018-11-29 14:52:52

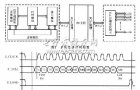

PCI總線接口的開發(fā)提供了一種簡(jiǎn)潔的方法,設(shè)計(jì)者只需設(shè)計(jì)出本地總線接口控制電路,即可實(shí)現(xiàn)與PCI總線的高速數(shù)據(jù)傳輸。圖3是應(yīng)用PCI9054作為接口芯片,開發(fā)PCI總線擴(kuò)展卡的總體硬件框架圖 下面簡(jiǎn)單

2018-12-05 10:12:42

框架圖,最后給出一個(gè)簡(jiǎn)單的實(shí)例。關(guān)鍵詞:PCI總線;局部總線;PCI9054一、 引言PCI 總線是英特爾公司推出的一種高性能局部總線,其數(shù)據(jù)總線為32 位,且可擴(kuò)展成64 位,最大數(shù)據(jù)傳輸速率為

2008-10-09 11:23:38

有哪位大神用過pci ip核,為什么輸入lm_req32請(qǐng)求,pci側(cè)沒有reqn請(qǐng)求輸出呢?

2016-06-27 17:56:59

/s的傳輸速率。PCI9052對(duì)9052編程可實(shí)現(xiàn)復(fù)用/非復(fù)用的8位、16位、32位的本地總線接口。同時(shí)它還具有內(nèi)部FIFO可以加速本地總線的操作。

2021-04-15 07:02:21

-----PCI9030制作了一個(gè)PCI接口卡。經(jīng)反復(fù)調(diào)試,該接口電路能夠順利地完成數(shù)據(jù)傳輸,已經(jīng)成功地實(shí)現(xiàn)PCI總線與外設(shè)的連接,這一方面驗(yàn)證了用專用接口芯片實(shí)現(xiàn)PCI總線接口在技術(shù)上的可行性

2019-05-05 09:29:33

與RTL8139的接口解決方案已在試驗(yàn)中得到實(shí)現(xiàn),并已用于IP分組語音數(shù)據(jù)的以太網(wǎng)傳輸,效果良好。隨著ISA總線的淘汰,PCI接口的網(wǎng)絡(luò)控制器必將在嵌入式領(lǐng)域中得到更廣泛的應(yīng)用。

2009-09-19 09:43:24

PCI Express的高級(jí)特性包括哪些?實(shí)現(xiàn)PCI Express接口的難點(diǎn)有哪些?FPGA的PCI Express接口有哪些優(yōu)勢(shì)?

2021-05-26 06:52:48

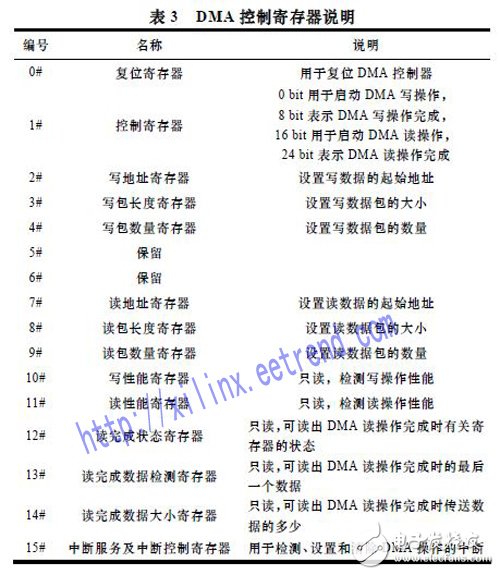

TLP格式,并傳送給發(fā)送引擎;接收引擎用于從PCIE IP核接收不同類型的TLP數(shù)據(jù),接收DMA控制模塊用于實(shí)現(xiàn)存儲(chǔ)器讀請(qǐng)求包的發(fā)送流量控制及接收數(shù)據(jù)位寬的轉(zhuǎn)換;DMA狀態(tài)控制寄存器模塊主要用來解析來自

2019-12-26 10:46:09

qsys設(shè)計(jì) avalon-mm 的硬IP核中斷是怎么實(shí)現(xiàn)的? 其中那個(gè)地址轉(zhuǎn)換表是有什么作用?

2020-10-28 13:59:22

100 MHz采樣速率和雙字節(jié)以內(nèi)的采樣精度的傳輸帶寬。目前,實(shí)現(xiàn)PCI Express總線接口控制的方法有兩種:一種是采用FPGA/CPLD來實(shí)現(xiàn)。目前,Altera等專業(yè)FPGA公司都提供了多種PCI

2019-06-11 05:00:06

傳輸,實(shí)現(xiàn)了系統(tǒng)設(shè)計(jì)的目標(biāo)。選擇PCI總線可以保證在足夠的帶寬下進(jìn)行數(shù)據(jù)傳輸。FPGA的應(yīng)用易于在線升級(jí)電路,擴(kuò)充平臺(tái)的功能。IP核的使用使硬件電路更為簡(jiǎn)潔、可靠。經(jīng)過驗(yàn)證,本文設(shè)計(jì)的系統(tǒng)可以很好地實(shí)現(xiàn)

2012-11-28 15:38:05

,并實(shí)現(xiàn)上下之間的接口以協(xié)調(diào)數(shù)據(jù)的傳送。管理器提供信號(hào)緩沖,能在高時(shí)鐘頻率下保持高性能,適合為顯卡,聲卡,網(wǎng)卡,MODEM等設(shè)備提供連接接口,工作頻率為33MHz/66MHz。 PCI總線系統(tǒng)要求有一

2009-05-03 22:15:14

本文的應(yīng)用背景為某一工業(yè)測(cè)控系統(tǒng),該系統(tǒng)采用FPGA實(shí)現(xiàn)測(cè)量數(shù)據(jù)的采集和控制信號(hào)的輸出,通過定制PCI接口IP實(shí)現(xiàn)一個(gè)32位目標(biāo)設(shè)備的PCI總線接口轉(zhuǎn)換。PCI核選用AlteraPCI編譯器所包括

2018-12-04 10:35:21

引言隨著半導(dǎo)體技術(shù)的發(fā)展,深亞微米工藝加工技術(shù)允許開發(fā)上百萬門級(jí)的單芯片,已能夠?qū)⑾到y(tǒng)級(jí)設(shè)計(jì)集成到單個(gè)芯片中即實(shí)現(xiàn)片上系統(tǒng)SoC。IP核的復(fù)用是SoC設(shè)計(jì)的關(guān)鍵,但困難在于缺乏IP核與系統(tǒng)的接口

2019-06-11 05:00:07

可以利用板上PROTOTYPE區(qū)實(shí)現(xiàn)用戶邏輯的功能。PCI開發(fā)板演示軟件可以顯示數(shù)據(jù)傳輸速率,也可用于調(diào)試,配置PCI Core。 基于IP模塊的PCI設(shè)計(jì)為用戶在FPGA目標(biāo)器件上實(shí)現(xiàn)PCI接口

2019-04-17 07:00:06

可以利用板上PROTOTYPE區(qū)實(shí)現(xiàn)用戶邏輯的功能。PCI開發(fā)板演示軟件可以顯示數(shù)據(jù)傳輸速率,也可用于調(diào)試,配置PCI Core。 基于IP模塊的PCI設(shè)計(jì)為用戶在FPGA目標(biāo)器件上實(shí)現(xiàn)PCI接口

2019-04-12 07:00:11

基于PCI Express的數(shù)據(jù)采集卡PCIe數(shù)據(jù)采集卡PCI Express數(shù)據(jù)采集卡本人在北京工作6年以上,從事FPGA外圍接口設(shè)計(jì),非常熟悉PCI Express協(xié)議,設(shè)計(jì)調(diào)試了多個(gè)基于PCI

2014-03-20 22:58:55

性,因此本文選擇了PCI總線。33MHz、32位的PCI總線的數(shù)據(jù)傳輸速率最高可達(dá)133MBps, 完全可以滿足高速實(shí)時(shí)傳輸的需求。選擇了Altera公司的PCI編譯器軟件包來實(shí)現(xiàn)PCI接口控制電路

2018-12-07 10:34:34

, 因此如何來實(shí)現(xiàn)該監(jiān)控系統(tǒng)中大量數(shù)據(jù)的高效、快速、準(zhǔn)確地采集和傳輸成為設(shè)計(jì)該監(jiān)控系統(tǒng)所面臨的一個(gè)主要難題。而本文所研究的基于PCI 總線的高速數(shù)據(jù)通信卡的設(shè)計(jì)正是解決上述難題的關(guān)鍵技術(shù)之一。PCI

2010-09-22 08:51:09

通道、奇偶校驗(yàn)和重試模塊組成。PCI從設(shè)備接口實(shí)現(xiàn)的功能是將一個(gè)不符合PCI總線協(xié)議的設(shè)備橋接到PCI總線上,為計(jì)算機(jī)PCI總線和用戶應(yīng)用之間傳輸數(shù)據(jù)提供一個(gè)數(shù)據(jù)通道。該從設(shè)備接口為用戶提供了一個(gè)簡(jiǎn)單

2019-05-29 05:00:02

功能描述及參數(shù)設(shè)置按照PCIE協(xié)議的要求,該FPGA的IP核也采用三層體系結(jié)構(gòu),即傳輸層、數(shù)據(jù)鏈路層和物理層。這三層功能模塊完成了PCIE的協(xié)議轉(zhuǎn)換,在傳輸層上給開發(fā)人員提供了非常豐富的接口。開發(fā)人員

2019-05-21 05:00:02

的協(xié)議軟件之間傳輸包字節(jié)流的信息,它們?cè)谛盘?hào)層被編碼成NRZI位信息后傳送出去。數(shù)據(jù)傳輸層用來實(shí)現(xiàn)在USB主機(jī)端的客戶端驅(qū)動(dòng)程序和設(shè)備端的功能接口之間傳輸有一定意義的信息,這些信息在協(xié)議層被打包成包格式

2018-11-21 11:30:06

PCI Express總線是什么?如何去設(shè)計(jì)一種PCI Express接口?如何對(duì)PCI Express接口進(jìn)行仿真測(cè)試?

2021-05-21 06:54:27

Xilinx 官方提供的技術(shù)參數(shù)來實(shí)現(xiàn)對(duì) IP 核的寫控制。寫命令和寫數(shù)據(jù)總線介紹DDR3 SDRAM控制器IP

2022-02-08 07:08:01

信號(hào),為采編器提供不同的數(shù)字量信號(hào),并對(duì)回收后的存儲(chǔ)器進(jìn)行數(shù)據(jù)的讀取分析。以前地面測(cè)試系統(tǒng)中的上位機(jī)軟件系統(tǒng)和地面控制臺(tái)之間的通信是由USB接口來完成的,傳輸速率較低。為了解決大容量數(shù)據(jù)高速讀取的瓶頸問題,采用PCI Express總線來讀取數(shù)據(jù)。

2019-09-23 06:11:11

和制定PCIE 2.0的規(guī)范,將數(shù)據(jù)速率提高到5Gbps.并制定了相應(yīng)的眼圖和抖動(dòng)分析方法. PCI-Express規(guī)范的不同版本及其子規(guī)范有合起來有9個(gè)以上,往往使測(cè)試工程在對(duì)不同的PCIE實(shí)現(xiàn)選擇何種標(biāo)準(zhǔn)無所適從。

2009-04-08 08:32:33

方的總線封裝模塊再作為Master把這種內(nèi)部總線傳輸轉(zhuǎn)換成合法的OCP命令傳送給目標(biāo)IP核;其作為Slave方接收命令并執(zhí)行所要求的操作。每一個(gè)OCP接口都是可根據(jù)連接實(shí)體的要求進(jìn)行配置的(通過選擇

2018-12-11 11:07:21

怎么實(shí)現(xiàn)基于IP內(nèi)核的PCI總線接口設(shè)計(jì)?

2021-05-27 06:34:05

本文提出了一種新的包括PCI9054單周期讀、寫和存儲(chǔ)器映射傳輸的設(shè)計(jì),并討論了通用PCI總線高速數(shù)據(jù)采集卡的實(shí)現(xiàn)方案。

2021-06-08 06:28:30

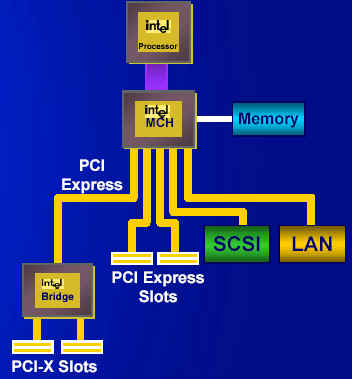

上下之間的接口以協(xié)調(diào)數(shù)據(jù)的傳送。PCI總線是一種樹型結(jié)構(gòu),并且獨(dú)立于CPU總線,可以和CPU總線并行操作。PCI總線上可以掛接PCI設(shè)備和PCI橋片,PCI總線上只允許有一個(gè)PCI主設(shè)備,其他的均為

2018-02-06 09:50:28

是基于PCI 總線的1553B 總線接口卡,要實(shí)現(xiàn)的功能是利用PCI 總線作為媒介, 實(shí)現(xiàn)計(jì)算機(jī)控制1553B 總線BC 端和RT 端進(jìn)行數(shù)據(jù)傳輸的功能,最終在衛(wèi)星地面測(cè)試過程中 實(shí)現(xiàn)由計(jì)算機(jī)對(duì)遠(yuǎn)程終端的設(shè)備

2019-05-21 05:00:22

如何實(shí)現(xiàn)基于IP模塊的PCI接口設(shè)計(jì)?

2021-04-20 06:28:50

操作系統(tǒng)中的實(shí)現(xiàn)有很大不同。首先,由于嵌入式處理器的時(shí)鐘頻率低,地址、數(shù)據(jù)總線窄,導(dǎo)致嵌入式系統(tǒng)對(duì)一個(gè)通用IP包的處理要花費(fèi)更多的處理機(jī)時(shí)間,從而影響其他任務(wù)的執(zhí)行,因此需要對(duì)龐大的復(fù)雜的TCP/IP

2019-04-28 09:57:18

的數(shù)據(jù)包,該ARP請(qǐng)求就是因?yàn)橐l(fā)送這個(gè)包而發(fā)送的。這種方法在假設(shè)上層會(huì)重發(fā)被覆蓋的數(shù)據(jù)時(shí)采用。每隔十秒鐘,表就會(huì)刷新一次,舊的記錄被丟棄,在嵌入式TCP/IP協(xié)議棧中,記錄的有效時(shí)間為1秒。 2.2.2

2019-04-23 07:00:10

用戶邏輯的功能。PCI開發(fā)板演示軟件可以顯示數(shù)據(jù)傳輸速率,也可用于調(diào)試,配置PCI Core。基于IP模塊的PCI設(shè)計(jì)為用戶在FPGA目標(biāo)器件上實(shí)現(xiàn)PCI接口提供了一種有效的途徑,設(shè)計(jì)工程師可以將主要精力

2019-05-08 07:00:46

的實(shí)時(shí)性,因此本文選擇了PCI總線。33MHz、32位的PCI總線的數(shù)據(jù)傳輸速率最高可達(dá)133MBps, 完全可以滿足高速實(shí)時(shí)傳輸的需求。選擇了Altera公司的PCI編譯器軟件包來實(shí)現(xiàn)PCI接口控制電路

2019-05-05 09:29:32

IP核來實(shí)現(xiàn)PCI接口,利用基于PCI協(xié)議的IP核來實(shí)現(xiàn)PCI接口,這種設(shè)計(jì)開發(fā)速度較快,靈活性較好,但是IP核價(jià)格昂貴。采用FPGA實(shí)現(xiàn)PCI總線協(xié)議。采用CPLD/FPGA等可編程邏輯器件實(shí)現(xiàn)PCI

2019-05-30 05:00:02

; PCI突發(fā)方式,133M字節(jié)/秒數(shù)據(jù)峰值傳送; 功能1,2 16C950高速串口IP核設(shè)計(jì) 完全VHDL源代碼設(shè)計(jì),標(biāo)準(zhǔn)接口模塊化設(shè)計(jì),可以移植到非PCI接口應(yīng)用; 軟件兼容16C550

2019-06-20 05:00:02

PCB設(shè)計(jì),使用獨(dú)立的外部時(shí)鐘同步芯片,可以為PCI及其它接口提供穩(wěn)定的零延遲時(shí)鐘系統(tǒng)電路,滿足PCI總線的時(shí)鐘要求,使驗(yàn)證平臺(tái)高速,穩(wěn)定,可靠的工作。 S1500硬件驗(yàn)證板照片以下為IP核驗(yàn)證平臺(tái)提供

2019-06-12 05:00:07

的PCI總線速度更快(數(shù)據(jù)傳輸率為133 Mb/s)、實(shí)時(shí)性更好、可控性更佳,更易于實(shí)現(xiàn)高速實(shí)時(shí)的I/O口控制卡、通信接口卡、數(shù)據(jù)采集卡等。但PCI總線也因其32位地址與數(shù)據(jù)復(fù)用、控制總線及時(shí)序較復(fù)雜

2019-04-29 07:00:09

核處理器NIOSⅡ作為系統(tǒng)的主控制器,結(jié)合ARINC429專用器件和其他外圍設(shè)備實(shí)現(xiàn)數(shù)據(jù)的收發(fā)功能。 ARI NC429接口板由數(shù)據(jù)收發(fā)、存儲(chǔ)器擴(kuò)展、監(jiān)控、PCI總線接口等模塊組成。NIOSⅡ控制

2019-04-26 07:00:08

控制器、PCI接口等等設(shè)計(jì)成可修改參數(shù)的模塊,讓其它用戶可以直接調(diào)用這些模塊,以避免重復(fù)勞動(dòng)。隨著CPLD/FPGA的規(guī)模越來越大,設(shè)計(jì)越來越復(fù)雜,使用IP核是一個(gè)發(fā)展趨勢(shì)。許多公司推薦使用現(xiàn)成的或經(jīng)過

2019-04-12 07:00:09

pci express標(biāo)準(zhǔn)中文版

PCI Express是新一代的總線接口,而采用此類接口的顯卡產(chǎn)品,已經(jīng)在2004年正式面世。早在2001年的春季“英特爾開發(fā)者論壇”上,英特爾公司就提出了要

2007-11-05 09:10:30 0

0 介紹 PCI 總線的特點(diǎn),對(duì)現(xiàn)有的 PCI 總線的接口設(shè)計(jì)方法進(jìn)行分析;介紹 PCI 接口芯片CY7C09449PV的結(jié)構(gòu)及其與數(shù)字信號(hào)處理器TMS320C32之間接口電路的設(shè)計(jì),提出一種基于PCI和 C32的數(shù)據(jù)

2009-04-08 09:53:42 26

26 基于PCI-Express的高速數(shù)據(jù)交換設(shè)計(jì)及應(yīng)用:摘要: 提出了利用PCIE總線技術(shù)實(shí)現(xiàn)數(shù)據(jù)高速傳輸的方案,結(jié)合共享內(nèi)存、DMA等技術(shù)設(shè)計(jì)了基于PCI鄄Express總線的高速數(shù)據(jù)傳輸卡,實(shí)現(xiàn)

2009-05-26 23:36:45 33

33 基于FPGA的PCI總線接口設(shè)計(jì)::PCI是一種高性能的局部總線規(guī)范,可實(shí)現(xiàn)各種功能標(biāo)準(zhǔn)的PCI總線卡。本文簡(jiǎn)要介紹了PCI總線的特點(diǎn)、信號(hào)與命令,提出了一種利用高速FPGA實(shí)現(xiàn)PCI總線接

2009-06-25 08:17:18 48

48 PCI 總線接口控制器的設(shè)計(jì)是基于PCI總線的應(yīng)用設(shè)計(jì)的關(guān)鍵所在。本文在介紹PCI9054接口控制器的基礎(chǔ)上,給出了一種通用的高速數(shù)據(jù)采集接口的設(shè)計(jì),并提出了一種新的包括PCI9054單

2009-07-30 15:33:13 18

18 PCI 總線是先進(jìn)的高性能32/64 位局部總線,成為微機(jī)總線標(biāo)準(zhǔn)。PCI 總線接口設(shè)計(jì)較其它總線接口設(shè)計(jì)復(fù)雜,本文討論了接口設(shè)計(jì)的方案,選擇CH365 作為接口芯片,描述了數(shù)據(jù)采集

2009-08-19 10:19:55 27

27 PCI Express是一種更高性能的第三代I/O總線。相對(duì)于傳統(tǒng)的PCI總線,它具有高速、低引腳數(shù)、點(diǎn)對(duì)點(diǎn)傳輸的特點(diǎn),使得該總線非常適合應(yīng)用于高速數(shù)據(jù)采集系統(tǒng)。對(duì)于記錄高速的合成孔

2009-08-31 11:35:53 26

26 本文簡(jiǎn)要介紹了PCI 總線的仲裁機(jī)制, 完成了PCI 總線仲裁器核心的設(shè)計(jì)、實(shí)現(xiàn)。通過ModelSim 進(jìn)行了軟件仿真,最后在XILINX 公司的FPGA 上加以了驗(yàn)證。

2009-09-03 08:18:29 27

27 本文通過一套數(shù)據(jù)采集卡的設(shè)計(jì)介紹了PCI 總線數(shù)據(jù)傳輸的基本過程,給出了系統(tǒng)整體設(shè)計(jì)方案和PCI 接口通信方式及驅(qū)動(dòng)程序實(shí)現(xiàn),并著重討論了PCI 數(shù)據(jù)傳輸中影響傳輸速率的

2009-09-21 10:19:54 34

34 針對(duì)可編程PCI Express解決方案的評(píng)估方法:外設(shè)部件互連( PCI )及其衍生的PCI - X和PCI Express是業(yè)界最常用的總線接口。PCI Express采用串行器/ 解串器(SERDES)接口為用戶提供今后應(yīng)用

2010-03-03 10:36:20 14

14 PCI Express 至PCI 橋設(shè)計(jì)原理及應(yīng)用

功能一般功能• PCI Express 至 PCI 橋• 透明、非透明及不透明模式• 有效的排隊(duì)及緩沖,實(shí)現(xiàn)

2010-03-06 11:16:26 35

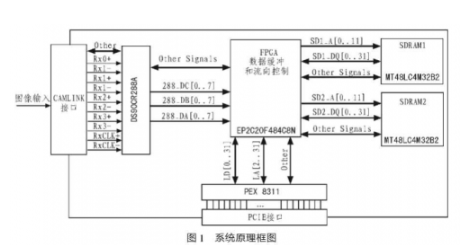

35 本文介紹一種基于PCI Express 總線的高速數(shù)據(jù)采集卡的設(shè)計(jì)方案及功能實(shí)現(xiàn)。給出系統(tǒng)的基本結(jié)構(gòu)及單元組成,重點(diǎn)闡述系統(tǒng)硬件設(shè)計(jì)的關(guān)鍵技術(shù)和本地總線的控制邏輯,詳細(xì)探

2010-09-22 08:15:04 62

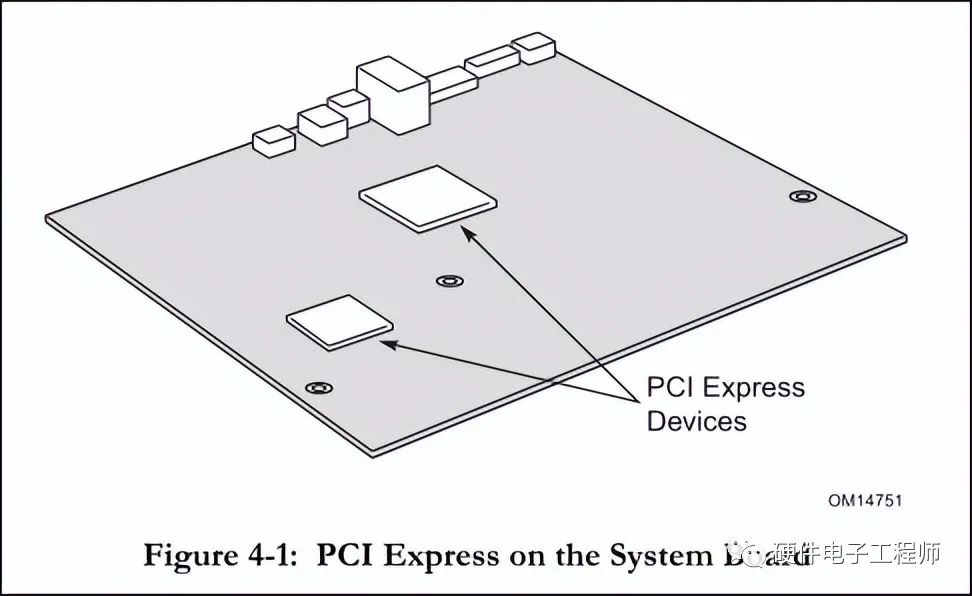

62 PCI-Express*概覽

Intel® Developer Network for PCI Express* Architectur

2006-12-25 15:10:22 1621

1621

瑞薩科技(Renesas Technology)宣布開發(fā)符合PCI Express Base Specification Revision 2.0 (PCI Express 2.0)高速串行接口標(biāo)準(zhǔn)之邏輯層與實(shí)體層之IP。整合此IP的LSI將能輕易地與其它支持PCI Express 2.0標(biāo)準(zhǔn)之

2009-01-05 16:23:24 553

553 PCI Express插槽,什么是PCI Express插槽,PCI Express插槽外形圖

PCI-Express是最新的總線和接口標(biāo)準(zhǔn),它原來的名稱為“3GIO”,是由英特爾提出的,很明顯英特

2009-04-26 18:19:16 4915

4915 摘 要 :PCI是一種高性能的局部總線規(guī)范,可實(shí)現(xiàn)各種功能標(biāo)準(zhǔn)的PCI總線卡。本文簡(jiǎn)要介紹了PCI總線的特點(diǎn)、信號(hào)與命令,提出了一種利用高速FPGA實(shí)現(xiàn)PCI總線接口的

2009-06-20 13:13:28 936

936

凌華科技率先發(fā)布亞洲首款PCI Express接口高速DIO卡PCIe-7350

凌華科技推出亞洲第一款PCI Express高速數(shù)字I/O卡PCIe-7350,它是全亞洲第一款數(shù)據(jù)傳輸量高達(dá)2

2009-08-05 09:25:19 727

727 PCI Express總線技術(shù)白皮書

1.1 PCI Express總線的起源和現(xiàn)狀 2001年春季的IDF上Intel正式公布PCI Express,是取代PCI總線的第三代IO技術(shù),也稱為

2009-10-04 09:39:14 1031

1031

基于Virtex5的PCI-Express總線接口設(shè)計(jì)

PCI Express是由Intel,Dell,Compaq,IBM,Microsoft等PCI SIG聯(lián)合成立的Arapahoe Work Group共同草擬并推舉成取代PCI總線標(biāo)準(zhǔn)的

2009-10-05 10:25:20 910

910

PCI總線接口技術(shù)及其在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

一種基于PCI總線的高速數(shù)據(jù)采集傳輸系統(tǒng)的實(shí)現(xiàn),討論了PCI總線控制器9054的性能及三種傳輸模式,

2009-12-08 14:39:06 1016

1016

PCI-Express插槽

PCI-Express是最新的總線和接口標(biāo)準(zhǔn),它原來的名稱為“3GIO”,是由英特爾提出的,很明顯英特爾的意思是它代表著下一代I/O接口標(biāo)準(zhǔn)。交由PCI-SIG(PCI

2009-12-24 15:19:51 461

461 什么是PCI Express接口 PCI Express(以下簡(jiǎn)稱PCI

2009-12-25 10:32:47 2505

2505 PCI Express總線

其實(shí),PCI Express是一個(gè)計(jì)算機(jī)系統(tǒng)總線的名稱,不過大家聽得最多的還是“接口”這個(gè)詞,也沒錯(cuò),PCI Express的確是下一

2010-01-22 11:21:51 627

627 PCI總線目標(biāo)接口芯片PCI9052及其應(yīng)用

摘要:PCI9052是PLX公司繼PCI9050之后新推出的一種低成本的PCI總線目標(biāo)接口芯片,它傳輸速率高,數(shù)據(jù)吞吐量大,

2010-03-03 19:21:58 2494

2494

為了實(shí)現(xiàn)FPGA 與PC 之間高速數(shù)據(jù)的雙向同時(shí)傳輸,設(shè)計(jì)了采用PCI 接口實(shí)現(xiàn)的雙向高速傳輸系統(tǒng)。系統(tǒng)中采用PCI9054 作為PCI 接口芯片連接PCI 總線與FPGA ,并通過PCI 驅(qū)動(dòng)程序的設(shè)計(jì)來提高數(shù)據(jù)

2011-05-14 11:08:23 34

34 本文提出了一種基于PCI Express總線接口的、具備可擴(kuò)展性能、并可大容量存儲(chǔ)數(shù)據(jù)的采集系統(tǒng)。該系統(tǒng)的最高采樣速率可達(dá)80 MHz,利用計(jì)算機(jī)并通過PCI Express總線和采集卡、Raid磁盤陣列相

2011-08-31 15:02:16 1851

1851

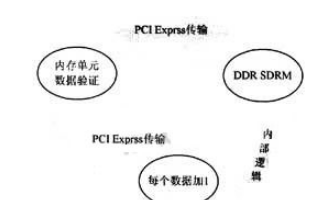

系統(tǒng)硬件部分負(fù)責(zé)采集前端高速LVDS數(shù)據(jù)并通過PCI Express總線傳輸給計(jì)算機(jī),以Xilinx公司MLS05開發(fā)板為實(shí)現(xiàn)載體,通過在Virtex-5 FPGA中設(shè)計(jì)邏輯實(shí)現(xiàn)高性能的DMA傳輸。FPGA中邏輯由Endpoint Bl

2011-09-01 16:26:55 49

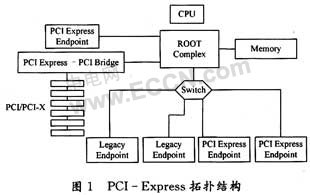

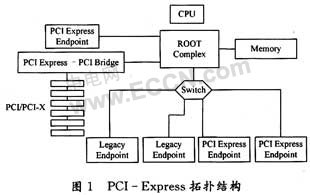

49 PCIE(PCI express)是用來互聯(lián)諸如計(jì)算機(jī)和通信平臺(tái)應(yīng)用中外圍設(shè)備的第三代高性能I/0總線。PCIE體系結(jié)構(gòu)繼承了第二代總線體系結(jié)構(gòu)最有用的特點(diǎn),采用與PCI相同的使用模型和讀/寫通信模

2011-10-17 16:14:20 1026

1026

出了一種PCI總線從設(shè)備的CPLD實(shí)現(xiàn)方法。該方法遵從PCI規(guī)范2.2版,實(shí)現(xiàn)了資源自動(dòng)配置并且支持數(shù)據(jù)突發(fā)傳輸。試驗(yàn)證明該方法的有效性,其突發(fā)傳輸速率可達(dá)20 MBs -1 。

2011-11-30 17:06:11 60

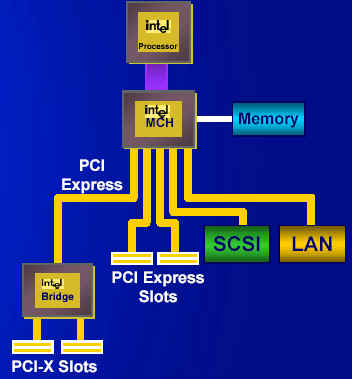

60 本內(nèi)容介紹了PCI總線/PCI-X接口及PCI-PCI-Express的知識(shí),講解了從PCI、PCI-X到PCI-Express之間的連接

2012-06-05 16:16:58 3084

3084

Xilinx FPGA工程例子源碼:PCI Express IP核應(yīng)用參考設(shè)計(jì)

2016-06-07 14:13:43 14

14 Xilinx FPGA工程例子源碼:PCI總線IP核(華為的商用)

2016-06-07 14:54:57 30

30 本文基于Xilinx公司的PCI Express IP核,為光纖通道HBA卡成功設(shè)計(jì)并實(shí)現(xiàn)了DMA引擎。

2017-10-11 11:09:11 8

8 采用IP核的設(shè)計(jì)方法,將外設(shè)組件互連標(biāo)準(zhǔn)(PCI)總線接口與具體功能應(yīng)用集成在一個(gè)FPGA上芯片, 提高了系統(tǒng)的集成度。在對(duì)PCI IP核進(jìn)行概述的基礎(chǔ)上,介紹了IP核的設(shè)計(jì)方法,實(shí)現(xiàn)了PCI總線

2017-11-17 12:27:03 4488

4488

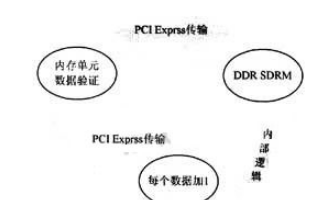

,推廣PCIE總線在嵌入式系統(tǒng)等場(chǎng)合的應(yīng)用,本文 設(shè)計(jì)了一款基于FPGA的PCIE數(shù)據(jù)傳輸系統(tǒng),為應(yīng)用PCIE進(jìn)行數(shù)據(jù)傳輸提供了一種新的低成本方案。 本文在對(duì)PCIE協(xié)議深入研究的基礎(chǔ)上,采用自頂向下的設(shè)計(jì)思想,對(duì)PCIE數(shù)據(jù)傳輸系統(tǒng)進(jìn)行頂層設(shè)計(jì)和模塊劃分,根據(jù)PCIE IP接口完成

2017-11-28 17:37:45 13

13 PCIExpress總線是新一代的I/O局部總線標(biāo)準(zhǔn),是取代PCI總線的革命性總線架構(gòu)。PCI總線曾經(jīng)是PC體系結(jié)構(gòu)發(fā)展史上的一個(gè)里程碑,但是隨著技術(shù)的不斷發(fā)展,新涌現(xiàn)出的一些外部設(shè)備對(duì)傳輸速度和帶寬有更高的要求,PCI設(shè)計(jì)之初并沒有考慮這些因素,因此并不能完全滿足這些外部設(shè)備的需求。

2018-04-11 16:00:00 6913

6913

了解UltraScale PCI Express解決方案的四個(gè)主要數(shù)據(jù)接口如何運(yùn)行。

具有四個(gè)獨(dú)立的數(shù)據(jù)接口簡(jiǎn)化了用戶設(shè)計(jì)并提高了整體PCI Express性能。

2018-11-29 06:43:00 3350

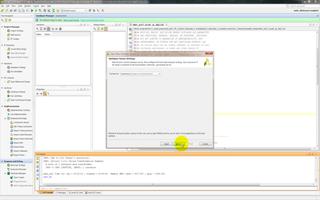

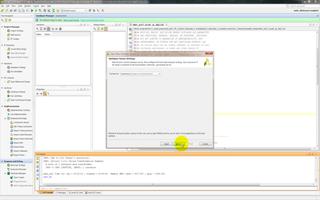

3350 了解如何創(chuàng)建和使用Xilinx的UltraScale PCI Express解決方案。

使用Vivado IP目錄GUI創(chuàng)建和使用PCI Express IP內(nèi)核。

打開示例設(shè)計(jì)并在Vivado軟件中實(shí)現(xiàn)它。

2018-11-28 06:36:00 3424

3424

和x32的數(shù)據(jù)帶寬。x1的通道能實(shí)現(xiàn)單向312.5 MB/s(2.5 Gb/s)的傳輸速率。Xilinx公司的Virtex5系列FPGA芯片內(nèi)嵌PCI-ExpressEndpoint Block硬核,為實(shí)現(xiàn)單片可配置PCI-Express總線解決方案提供了可能。

2020-01-19 16:52:00 787

787

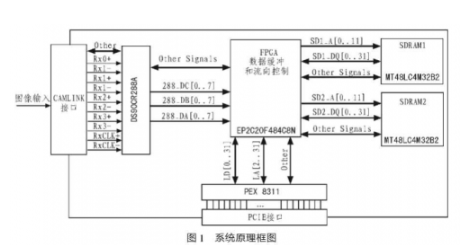

圖像采集和處理技術(shù)在機(jī)器視覺和圖像分析等諸多領(lǐng)域應(yīng)用十分廣泛。隨著高速的 PCI Express(PCIE)總線的出現(xiàn),基于 PCIE 接口的高速數(shù)據(jù)采集卡將在數(shù)據(jù)傳輸和處理量很大的場(chǎng)合發(fā)揮越來越重要的作用。

2020-07-16 17:02:04 2900

2900

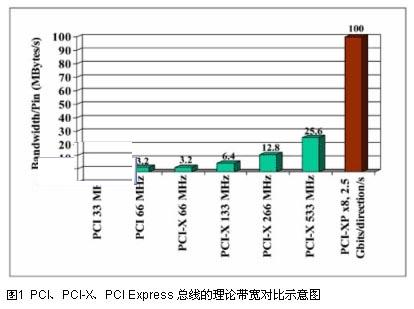

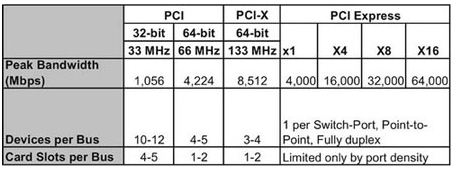

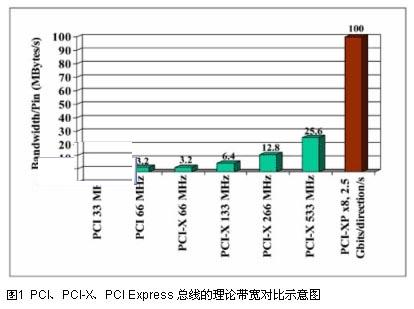

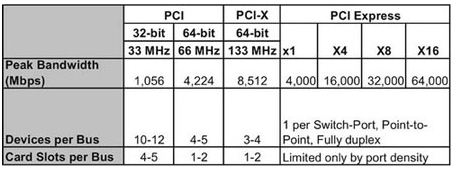

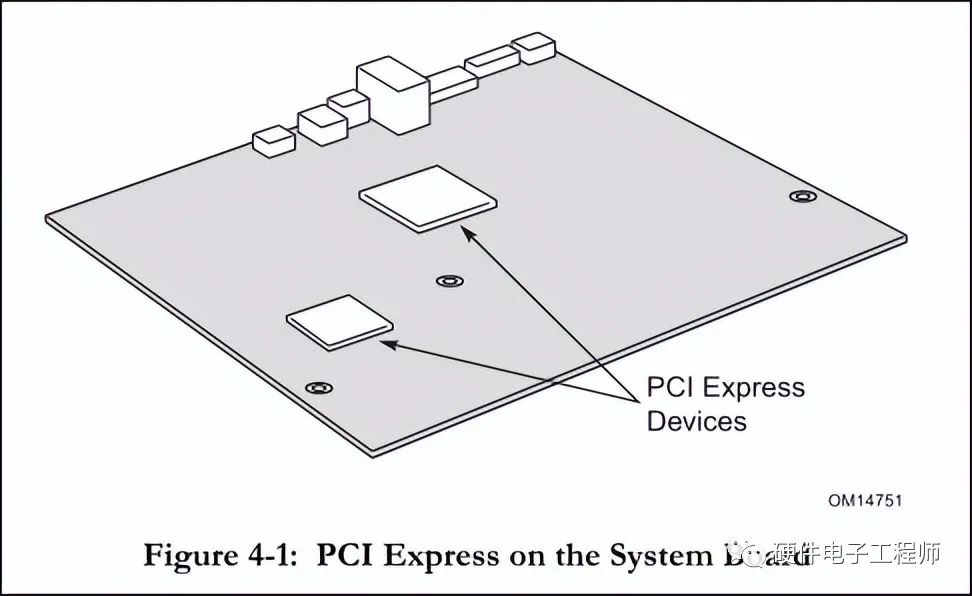

PCI Express是從PCI發(fā)展而來的一種系統(tǒng)互聯(lián)接口標(biāo)準(zhǔn)。PCI和PCI-X都是基于32位以及64位的并行總線,而PCI Express則使用高速串行總線。PCI Express后向兼容于PCI,能夠靈活地提供大峰值帶寬。表1對(duì)比了三種PCI標(biāo)準(zhǔn)的特性。

2021-06-18 10:53:00 2187

2187

PCIe接口全稱PCI Express,由PCI-SIG組織發(fā)布的用于替代PCI總路線的新一代高速串行總線與接口。

2023-06-25 16:27:04 6189

6189

PCIe接口全稱PCI Express,由PCI-SIG組織發(fā)布的用于替代PCI總路線的新一代高速串行總線與接口。

2023-07-22 16:52:50 5905

5905

PCI總線協(xié)議非常復(fù)雜,目前實(shí)現(xiàn)PCI接口的有效方案分為兩種:即使用可編程邏輯器件和使用專用總線接口的器件,可編程邏輯器件實(shí)現(xiàn)PCI接口比較靈活,可以利用的器件比較多,現(xiàn)在有許多生產(chǎn)可編程邏輯器件的廠商(如Xilinx的Logicore和Alerra的AMPP)都提供經(jīng)過嚴(yán)格測(cè)試的PCI接口功能模塊

2023-08-01 14:37:19 553

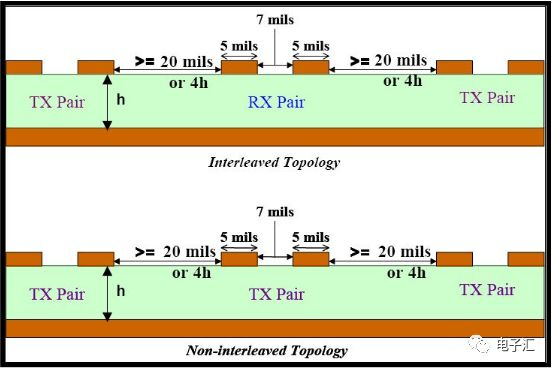

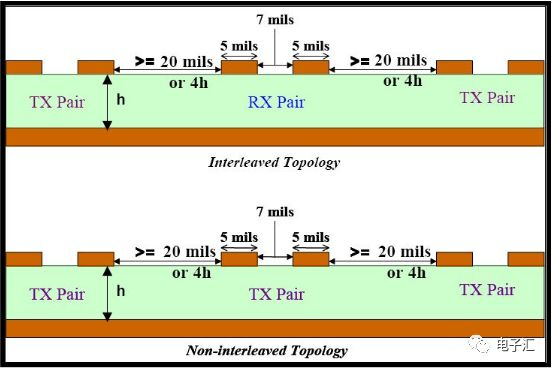

553 PCI-Express總線接口的布線規(guī)則

2023-11-29 15:49:58 492

492

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論