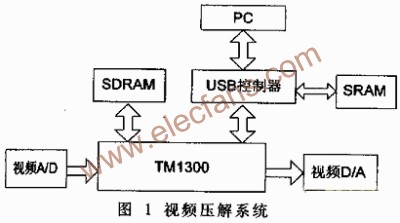

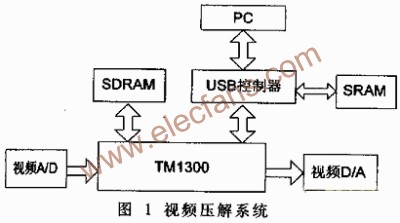

本文針對高速數(shù)據(jù)傳輸需求,根據(jù)USB2.0的協(xié)議規(guī)范,利用VHDL語言實現(xiàn)符合該協(xié)議的功能控制器,在視頻壓解系統(tǒng)中使數(shù)據(jù)在PC與外設(shè)之間高速傳輸。

2010-10-28 15:44:03 1170

1170

vhdl語言實現(xiàn)16位數(shù)據(jù)通信,求助!

2014-03-07 14:02:47

希望在今后的學(xué)習(xí)中大家多多幫助,先來幾個基礎(chǔ)的verilog 教材吧 現(xiàn)在我用到了FPGA關(guān)鍵分配的知識。 不過還是想系統(tǒng)的學(xué)習(xí)一下。那就先從軟件的使用和語法開始學(xué)習(xí)吧。 完整的pdf格式文檔電子發(fā)燒友下載地址(共31頁): FPGA中文VHDL語言教程.pdf

2018-07-04 01:11:32

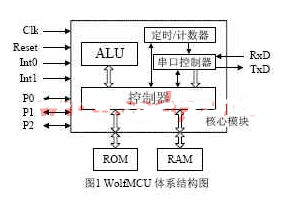

設(shè)計RISC微處理器需要遵循哪些原則?基于FPGA技術(shù)用VHDL語言實現(xiàn)的8位RISC微處理器

2021-04-13 06:11:51

的設(shè)計早期就能查驗設(shè)計系統(tǒng)的功能可行性,隨時可對設(shè)計進(jìn)行仿真模擬。3.大規(guī)模設(shè)計一些大型的 FPGA 設(shè)計項目必須有多人甚至多個開發(fā)組共同并行工作才能實現(xiàn)。VHDL 語句的行為描述能力和程序結(jié)構(gòu)決定了它具有

2018-09-07 09:04:45

本帖最后由 eehome 于 2013-1-5 09:51 編輯

VHDL語言100例詳解

2012-08-20 20:45:49

本帖最后由 田家二好 于 2015-3-20 11:52 編輯

VHDL語言100例詳解.pdf僅供學(xué)習(xí)

2015-03-17 21:54:30

VHDL語言100例詳解.pdf 僅供學(xué)習(xí)

2015-03-20 11:52:07

VHDL語言詳解(修正版)希望對需要的人有幫助

2013-06-28 13:00:18

,舉例說明了利用VHDL語言實現(xiàn)數(shù)字系統(tǒng)的過程。 整個數(shù)字電壓表的硬件結(jié)構(gòu)如圖1所示。 工作時,系統(tǒng)按一定的速率采集輸入的模擬電壓,經(jīng)ADC0804轉(zhuǎn)換為8位數(shù)字量,此8位數(shù)字量經(jīng)FPGA處理

2012-10-26 15:46:00

請教大家怎么用VHDL語言實現(xiàn)減法運算?在FPGA設(shè)計時又該怎么操作呢?

2012-05-17 20:07:12

如何用VHDL 語言實現(xiàn)右移位啊?求大神幫看看為什么實現(xiàn)不了右移位?library ieee;use ieee.std_logic_1164.all;use

2016-05-28 15:46:38

vhdl語言實例大全下載

2008-05-20 09:36:01

我使用ADUC7061做的信號采集,現(xiàn)在客戶需要實現(xiàn)EEPROM功能來保存3-5個數(shù)據(jù),請問如何使用C語言實現(xiàn)?不使用外部EEPROM 專用IC。

2024-01-12 06:56:45

C++語言實現(xiàn)火車排序功能.doc

2017-08-05 22:01:19

C語言實現(xiàn)常用排序算法是什么?

2021-10-19 06:41:46

C語言實現(xiàn)的泛型函數(shù)swap():交換兩個變量中的數(shù)據(jù).

2022-01-20 07:10:47

CRC算法和c語言實現(xiàn)

2012-08-20 19:21:44

MicroPython是什么?TPYBoard是怎樣通過Python腳本語言實現(xiàn)單片機(jī)控制的?

2021-11-10 06:56:49

數(shù)字示波器的FPGA實現(xiàn), VHDL語言,測試通過(僅供參考)

2009-11-06 19:53:52

請問使用VHDL語言設(shè)計FPGA有哪些常見問題?

2021-05-06 09:05:31

ALU的基本結(jié)構(gòu)如圖2-4-1所示。我們用Robei(微信公眾號)所設(shè)計的ALU要實現(xiàn)最基本的加減運算,與或非和異或等功能。圖2-4-1 ALU基本結(jié)構(gòu)(1)加法運算包含2種類型,一種是不帶進(jìn)位的加法器

2015-04-13 15:03:00

在PSOC中,怎樣用C語言實現(xiàn)整型向字符型的轉(zhuǎn)換?

2012-11-19 15:43:46

不知道有沒有大神做過:基于FPGA的圖像邊緣檢測系統(tǒng)設(shè)計,用VHDL語言實現(xiàn)

2018-05-10 00:22:07

。FPGA芯片用米直接控制其他元件的工作,對小鍵盤的輸入,通過一定的算法實現(xiàn)電子密碼鎖的功能。通過控制ISD2560的控制腳的電平狀態(tài),達(dá)到控制其發(fā)音從而實現(xiàn)智能語音提示的效果。3個發(fā)光二極管分別用于顯示

2021-07-03 08:00:00

語言進(jìn)行CPLD/FPGA設(shè)計開發(fā),Altera和Lattice已經(jīng)在開發(fā)軟件方面提供了基于本公司芯片的強大開發(fā)工具。但由于VHDL設(shè)計是行為級設(shè)計,所帶來的問題是設(shè)計者的設(shè)計思想與電路結(jié)構(gòu)相脫節(jié),而且

2019-06-18 07:45:03

基于Proteus和C語言實現(xiàn)一共四個題目,有沒有人愿意嘗試一下?

2021-07-14 06:20:45

本文介紹應(yīng)用美國ALTERA公司的MAX+PLUSⅡ平臺,使用VHDL硬件描述語言實現(xiàn)的十六路彩燈控制系統(tǒng)。

2021-04-19 07:43:57

如何使用C語言實現(xiàn)模糊PID控制?

2021-09-24 08:54:18

利用現(xiàn)場可編程門陣列(FPGA)和VHDL 語言實現(xiàn)了PCM碼的解調(diào),這樣在不改變硬件電路的情況下,能夠適應(yīng)PCM碼傳輸速率和幀結(jié)構(gòu)變化,從而正確解調(diào)數(shù)據(jù)。

2021-05-07 06:58:37

本文介紹利用VHDL語言實現(xiàn) FPGA與單片機(jī)的串口異步通信電路。

2021-04-29 06:34:57

如何利用c語言實現(xiàn)中文“大”字的顯示?

2021-11-02 06:25:39

幀同步是什么工作原理?如何用VHDL語言實現(xiàn)幀同步的設(shè)計?

2021-04-08 06:33:59

關(guān)于用QuartusⅡ軟件實現(xiàn)編程調(diào)試,用VHDL語言描述該邏輯關(guān)系。多次嘗試編寫,并不能準(zhǔn)確描述邏輯關(guān)系,以及進(jìn)行編程調(diào)試,對于vhdl語言不能準(zhǔn)確應(yīng)用,想請教一下結(jié)構(gòu)體的相關(guān)邏輯語言。

2022-05-04 12:21:32

老大看到OOP編程很好,就讓我學(xué),怎么用C語言實現(xiàn)OOP編程的,請大俠指點

2019-10-30 03:45:28

、組合、多態(tài)等面向?qū)ο蟮?b class="flag-6" style="color: red">功能,但C語言有struct和函數(shù)指針。我們可以用struct中的數(shù)據(jù)和函數(shù)指針,以此來模擬對象和類的行為。所以在正式開始設(shè)計模式前,先看看如何用C語言實現(xiàn)面向?qū)ο缶幊獭1菊箩槍γ嫦驅(qū)ο蟮姆庋b、繼承、組合、多態(tài)給出C語言的實現(xiàn)方法。1.1 封裝封裝是指對象僅暴露必要的對外接口(這里

2021-07-12 07:24:18

各位大家好,我正在尋找用VHDL語言編寫的UDP / IP堆棧(我必須在Spartan-6 FPGA中實現(xiàn)它)。我正在尋找一個盡可能簡單的功能:使用VHDL語言編寫,而不是Verilog - 在

2019-08-06 02:37:22

小白求助,求基于Proteus和C語言實現(xiàn)的程序和仿真

2021-10-19 06:20:34

本人小菜鳥,開始學(xué)FPGA的時候?qū)W的Verilog語言,后來因為課題組前期的工作都是VHDL就該學(xué)VHDL了。最近聽了幾個師兄的看法,說國內(nèi)用VHDL的已經(jīng)很少了,建議我還是堅持用Verilog,小菜現(xiàn)在好糾結(jié),請問到底應(yīng)該用哪種語言呢?望各位大神指點!

2015-07-08 10:07:56

最近在做個課題,需要用FPGA中的verilog語言實現(xiàn)BPSK調(diào)制,fpga不是很會,望大神指導(dǎo)下,急求代碼啊!謝謝

2013-03-06 18:12:36

各位大神求救啊用verilog語言實現(xiàn)電子鐘

2014-05-04 16:37:51

用VHDL語言實現(xiàn)樂曲演奏電路本程序是用VHDL對《梁祝協(xié)奏曲》中《化蝶》部分的樂曲電路實現(xiàn)。

2011-08-18 10:31:53

VHDL硬件描述語言教學(xué):包括fpga講義,VHDL硬件描述語言基礎(chǔ),VHDL語言的層次化設(shè)計的教學(xué)幻燈片

2006-03-27 23:46:49 93

93 第1章 緒論 1.1 關(guān)于EDA 1.2 關(guān)于VHDL 1.3 關(guān)于自頂向下的系統(tǒng)設(shè)計方法 1.4 關(guān)于應(yīng)用 VHDL的 EDA過程 1.5 關(guān)于在系統(tǒng)編程技術(shù) 1.6 關(guān)于FPGA/CPLD的優(yōu)勢 1.7

2008-06-04 10:24:06 1679

1679

介紹了用VHDL 語言在硬件芯片上實現(xiàn)浮點加/ 減法、浮點乘法運算的方法,并以Altera

公司的FLEX10K系列產(chǎn)品為硬件平臺,以Maxplus II 為軟件工具,實現(xiàn)了6 點實序列浮點加/ 減法

2009-07-28 14:06:13 85

85 CRC算法原理及C語言實現(xiàn):本文從理論上推導(dǎo)出CRC 算法實現(xiàn)原理,給出三種分別適應(yīng)不同計算機(jī)或微控制器硬件環(huán)境的C 語言程序。讀者更能根據(jù)本算法原理,用不同的語言編寫出獨特

2009-09-23 23:38:50 31

31 用JAVA語言實現(xiàn)RSA公鑰密碼算法:本文闡述了公開密鑰密碼體制RSA算法的原理及實現(xiàn)技術(shù)。并在此基礎(chǔ)上,給出了JAVA語言實現(xiàn)的RSA算法源代碼。關(guān)鍵詞:ILSA體制;公鑰;密鑰

2010-02-10 10:27:15 58

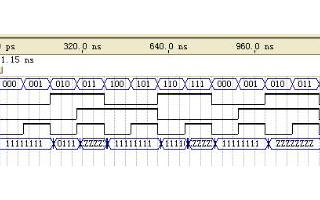

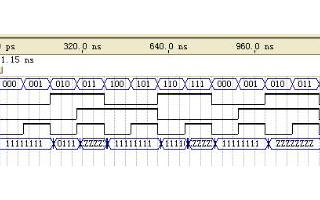

58 本文設(shè)計了一種在數(shù)字通信系統(tǒng)中的數(shù)字鎖相位同步提取方案,詳細(xì)介紹了本設(shè)計的位同步提取原理及其各個組成功能模塊的VHDL語言實現(xiàn),并在Quartus II開發(fā)平臺上仿真驗證通過。本

2010-08-06 14:28:08 64

64 設(shè)計和實現(xiàn)了一個以Altera FPGA的Cyclone器件EP1C6Q240C8為核心的多功能實驗板.它分為核心板和擴(kuò)展板, 用戶可以結(jié)合QuartusII集成開發(fā)環(huán)境, 使用VHDL語言、Verilog HDL語言或原理圖, 進(jìn)行編

2010-09-14 16:38:06 12

12 介紹了基于單片機(jī)、FPGA的網(wǎng)絡(luò)數(shù)據(jù)加密實現(xiàn)。整個系統(tǒng)由單片機(jī),FPGA和E1通信接口組成。流密碼加密算法采用A5/1和W7算法。采用VHDL硬件語言實現(xiàn)FPGA功能。該硬件加密系統(tǒng)具有較好

2010-12-24 16:26:54 27

27 用VHDL語言實現(xiàn)3分頻電路

標(biāo)簽/分類:

眾所周知,分頻器是FPGA設(shè)計中使用頻率非常高的基本設(shè)計之一,盡管在目前大部分設(shè)計中,廣泛使用芯片廠家集成的鎖相

2007-08-21 15:28:16 5527

5527 用C語言實現(xiàn)FFT算法

/*****************fft programe*********************/#include "typedef.h" #include "math.h"

struct compx EE(struct compx

2008-10-30 13:39:56 6179

6179 【摘 要】 通過設(shè)計實例詳細(xì)介紹了用VHDL(VHSIC Hardware DescriptionLanguage)語言開發(fā)FPGA/CPLD的方法,以及與電路圖輸入和其它HDL語言相比,使用VHDL語言的優(yōu)越性。

2009-05-10 19:47:30 1111

1111

用VHDL語言實現(xiàn)3分頻電路(占空比為2比1)

分頻器是FPGA設(shè)計中使用頻率非常高的基本設(shè)計之一,盡管在目前大部分設(shè)計中,廣泛使用芯片廠家集成的鎖

2009-06-22 07:46:33 7831

7831 基于VHDL語言的智能撥號報警器的設(shè)計

介紹了以EDA技術(shù)作為開發(fā)手段的智能撥號報警系統(tǒng)的實現(xiàn)。本系統(tǒng)基于VHDL語言,采用FPGA作為控制核心,實現(xiàn)了遠(yuǎn)程防盜報警。該

2009-10-12 19:08:43 1167

1167

采用CPLD/FPGA的VHDL語言電路優(yōu)化原理設(shè)計

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工業(yè)標(biāo)準(zhǔn)硬件描述語言,是隨著可編程邏輯器件(PLD)的發(fā)展而發(fā)展起

2010-03-19 11:38:02 2318

2318

基于現(xiàn)場可編程(FPGA)技術(shù)和硬件描述語言VHDL的設(shè)計和綜合,通過自頂向下的設(shè)計方法和模塊化設(shè)計思想,在Quartus II環(huán)境下能定制、仿真、下載驗證和實現(xiàn)CPU功能。通過VHDL語言定制了運算器ALU模塊和調(diào)用宏模塊定制了RAM模塊,介紹了基于FPGA的CPU設(shè)計方法,

2011-03-15 17:39:19 177

177 利用一塊芯片完成除時鐘源、按鍵、揚聲器和顯示器(數(shù)碼管)之外的所有數(shù)字電路功能。所有數(shù)字邏輯功能都在CPLD器件上用VHDL語言實現(xiàn)。這樣設(shè)計具有體積小、設(shè)計周期短(設(shè)計過

2011-09-27 15:08:56 366

366 該ALU采取層次化設(shè)計方法,由控制模塊、邏輯模塊、加減法模塊、乘法模塊和除法模塊組成,能實現(xiàn)32位有符號數(shù)和無符號數(shù)的加減乘除運算,另外還能實現(xiàn)9種邏輯運算、6種移位運算以

2012-02-09 15:24:55 80

80 DSP算法的c語言實現(xiàn),又需要的朋友下來看看。

2016-05-09 10:59:26 0

0 Xilinx FPGA工程例子源碼:FM收音機(jī)的解碼及控制器VHDL語言實現(xiàn)

2016-06-07 14:13:43 11

11 卡爾曼濾波算法C語言實現(xiàn) 可以運行STM32 和 arduino上 已測試成功

2016-09-27 16:34:16 67

67 C++語言實現(xiàn)火車排序功能

2017-01-05 11:27:10 2

2 基于FPGA/CPLD的UART功能設(shè)計

2017-01-23 20:45:37 30

30 介紹了VHDL語言的特點及優(yōu)勢,表明了EDA技術(shù)的先進(jìn)性,采用自上而下的設(shè)計思路,運用分模塊的設(shè)計方法設(shè)計了數(shù)字時鐘系統(tǒng),并在QuartusⅡ環(huán)境下進(jìn)行編譯和仿真,完成了24 h計時和輔助功能設(shè)計

2017-11-28 14:55:56 13

13 4個重要算法C語言實現(xiàn)源代碼

2018-06-10 08:00:00 12

12 VHDL是一種用來描述數(shù)字邏輯系統(tǒng)的“編程語言”。它通過對硬件行為的直接描述來實現(xiàn)對硬件的物理實現(xiàn),代表了當(dāng)今硬件設(shè)計的發(fā)展方向。VHDL是為了滿足邏輯設(shè)計過程中的各種需求而設(shè)計的。

2020-04-23 15:51:03 2362

2362

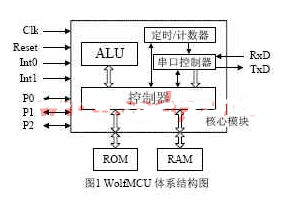

基于以上討論,可以看出ASIP+FPGA設(shè)計模式可以從很大程度上解決引言中提到的兩個難題。為了進(jìn)行更深入的研究,我們對該設(shè)計模式進(jìn)行了嘗試,用VHDL硬件描述語言在FPGA上實現(xiàn)了一個8位微處理器

2020-07-28 17:44:49 562

562

本文檔的主要內(nèi)容詳細(xì)介紹的是使用Quartus和VHDL語言實現(xiàn)的LPC時序的工程文件免費下載。

2020-09-18 16:49:00 20

20 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的VHDL語言100個實例詳解包括了:第1例帶控制端口的加法器,第2例元控制端口的加法器,第3例乘法器,第4例比較器,第5例二路選擇器,第6例寄存器

2020-12-21 17:10:53 63

63 本文檔的主要內(nèi)容詳細(xì)介紹的是基于VHDL硬件描述語言實現(xiàn)CPSK調(diào)制的程序及仿真。

2021-01-19 14:34:15 11

11 本文檔的主要內(nèi)容詳細(xì)介紹的是使用VHDL硬件描述語言實現(xiàn)基帶信號的MASK調(diào)制的程序與仿真。

2021-01-19 14:34:17 13

13 本文檔的主要內(nèi)容詳細(xì)介紹的是使用VHDL硬件描述語言實現(xiàn)基帶信號的MFSK調(diào)制的程序與仿真。

2021-01-19 14:34:19 4

4 本文檔的主要內(nèi)容詳細(xì)介紹的是如何使用VHDL硬件描述語言實現(xiàn)基帶信號的MPSK調(diào)制。

2021-01-19 14:34:21 2

2 本文檔的主要內(nèi)容詳細(xì)介紹的是使用VHDL硬件描述語言實現(xiàn)基帶碼發(fā)生器的程序設(shè)計與仿真免費下載。

2021-01-20 13:44:16 11

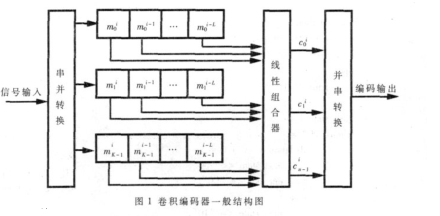

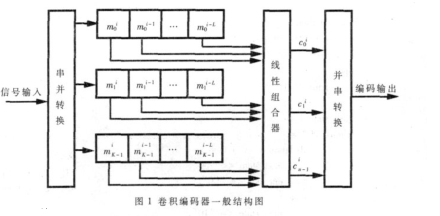

11 介紹并用VHDL語言實現(xiàn)了卷積編碼和維特比譯碼。根據(jù)編碼器特征設(shè)計了一種具有針對性的簡潔的維特比譯碼器結(jié)構(gòu),

2021-05-12 15:22:41 2112

2112

EDA技術(shù)使得電子線路的設(shè)計人員能在計算機(jī)上完成電路的功能設(shè)計、邏輯設(shè)計、時序測試直至印刷電路板的自動設(shè)計。本文介紹了以 VHDL 語言和硬件電路為表達(dá)方式,以 Quartus II 軟件為設(shè)計工具,最終通過 FPGA 器件實現(xiàn)數(shù)字時鐘的設(shè)計過程。

2021-05-25 16:28:10 35

35 關(guān)于Actel 的FPGA的譯碼器的VHDL源代碼(通信電源技術(shù)期刊2020年第14期)-關(guān)于Actel 的FPGA的譯碼器的VHDL源代碼。適合感興趣的學(xué)習(xí)者學(xué)習(xí),可以提高自己的能力,大家可以多交流哈

2021-09-16 15:18:01 10

10 CRC校驗算法原理及c語言實現(xiàn)

2021-11-30 10:04:07 8

8 累加校驗和C語言實現(xiàn)

2021-11-29 18:06:11 10

10 這里我想主要介紹下在C語言中是如何實現(xiàn)的面向?qū)ο蟆V懒薈語言實現(xiàn)面向?qū)ο蟮姆绞剑覀冊俾?lián)想下,C++中的class的運行原理是什么?

2022-10-12 09:12:27 1578

1578 設(shè)備的計劃運行時間來自于設(shè)備的班次模式,“生產(chǎn)日歷“模塊描述設(shè)備的計劃作息時間。關(guān)于“生產(chǎn)日歷”的功能設(shè)計和實現(xiàn),請參閱前文“MES工單管理功能設(shè)計和實現(xiàn)”中關(guān)于“工廠建模”中的詳細(xì)描述,其功能完全相同,此處不再贅述。

2023-05-25 15:21:19 609

609

本文介紹利用VHDL語言實現(xiàn)FPGA與單片機(jī)的串口異步通信電路。

2023-08-03 15:45:37 790

790

在這個項目中,我們用 VHDL 語言創(chuàng)建一個 8 位算術(shù)邏輯單元 (ALU),并在連接到帶有輸入開關(guān)和 LED 顯示屏的定制 PCB 的 Altera CPLD 開發(fā)板上運行。

2023-10-24 17:05:57 675

675

電子發(fā)燒友網(wǎng)站提供《基于VHDL語言實現(xiàn)遠(yuǎn)程防盜報警設(shè)計.pdf》資料免費下載

2023-11-08 14:33:11 0

0 功能,從而實現(xiàn)對數(shù)字電路的高效定制。FPGA語言主要包括VHDL(VHSIC Hardware Description Language)和Verilog等,這些語言具有強大的描述能力,能夠精確地定義硬件的每一個細(xì)節(jié),從而實現(xiàn)復(fù)雜的數(shù)字系統(tǒng)設(shè)計。

2024-03-15 14:50:26 166

166

電子發(fā)燒友App

電子發(fā)燒友App

評論