Xilinx All Programmable 平臺(tái)和解決方案可實(shí)現(xiàn)更出色的工業(yè)自動(dòng)化和工業(yè)成像應(yīng)用。Xilinx FPGA 和 Zynq-7000 All Programmable SoC 所具有

2013-01-23 14:45:16 1170

1170 電子設(shè)計(jì)競(jìng)賽使用到Xilinx 技術(shù)的參賽隊(duì)伍備注:研電賽官網(wǎng)報(bào)名時(shí)勾選參與Xilinx 企業(yè)專項(xiàng)獎(jiǎng)評(píng)選!不勾選則無(wú)法參加!!!獎(jiǎng)項(xiàng)設(shè)置獎(jiǎng)項(xiàng)設(shè)置數(shù)量獎(jiǎng)品最佳作品獎(jiǎng)110000元獎(jiǎng)金AI專項(xiàng)獎(jiǎng)110000元

2020-05-23 15:36:29

1 個(gè) AI 模型 = 5 輛汽車終身碳排量,AI 為何如此耗能?

2021-01-22 06:35:03

AI概念籠統(tǒng),范圍廣大,到底什么才是AI的核心?手把手教你設(shè)計(jì)人工智能芯片及系統(tǒng)(全階設(shè)計(jì)教程+AI芯片F(xiàn)PGA實(shí)現(xiàn)+開(kāi)發(fā)板)詳情鏈接:http://url.elecfans.com/u/c422a4bd15

2019-10-18 06:39:12

Xilinx Artix7 DEVB_124X92MM 6~16V

2023-03-28 13:05:55

大家好,我正在使用Xilinx ISE 14.7(針對(duì)Virtex5,因此沒(méi)有Vivado),并且遇到了工具的問(wèn)題,因此更改設(shè)計(jì)中的信號(hào)名稱會(huì)影響實(shí)現(xiàn),從而影響時(shí)序,在某些情況下會(huì)略有變化比如說(shuō),一

2018-11-02 11:14:38

哪位大神做過(guò)xilinx的PC-CFR算法的實(shí)現(xiàn),希望能指導(dǎo)一下!!!

2014-04-03 23:32:21

Xilinx TCP_IP協(xié)議實(shí)現(xiàn)

2012-08-17 09:03:39

。 2實(shí)現(xiàn) Xilinx 7系列的差分信號(hào)的實(shí)現(xiàn)主要通過(guò)IBUFDS、OBUFDS、IOBUFDS等原語(yǔ)的調(diào)用,在程序中直接進(jìn)行原語(yǔ)的例化,以IBUFDS和OBUFDS為例: 2.1IBUFDS

2020-12-23 17:17:47

大家好,我使用ram_style是“塊”來(lái)推斷塊RAM,如下所示。(* ram_style =“block”*)reg [8:0] ram_name [8191:0];運(yùn)行實(shí)現(xiàn)任務(wù)后,Vivado

2020-03-31 07:45:01

xilinx和altera區(qū)別分析1. 從好用來(lái)說(shuō),肯定是Xilinx的好用,不過(guò)Altera的便宜他們的特點(diǎn),Xilinx的短線資源非常豐富,這樣在實(shí)現(xiàn)的時(shí)候,布線的成功率很高,尤其是邏輯做得比較

2012-02-28 14:40:59

在 CPU 上推斷出 FP32 模型格式和 FP16 模型格式。

FP32 模型格式的推斷速度比 FP16 模型格式快。

無(wú)法確定推斷 FP32 模型格式的原因比 CPU 上的 FP16 模型格式快。

2023-08-15 08:03:04

ADAPTER TC2050 FOR XILINX CABLE

2023-03-22 19:59:52

我想知道 X-CUBE-AI 和 NanoEdge AI Studio 在 ML 和 AI 開(kāi)發(fā)環(huán)境中的區(qū)別。我可以在任何一個(gè)開(kāi)發(fā)環(huán)境中做同樣的事情嗎?使用的設(shè)備有什么限制嗎?

2022-12-05 06:03:15

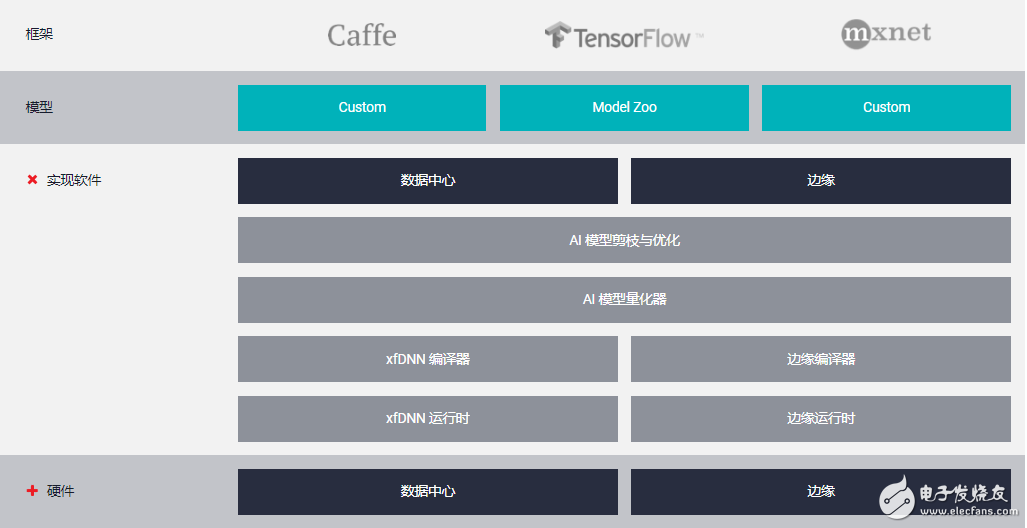

的 AI 推斷性能。主要特點(diǎn)包括:l為主流框架和最新模型提供支持,幫助其完成各種深度學(xué)習(xí)任務(wù),如 CNN、RNN 和 NLP 等l功能強(qiáng)大的量化器和優(yōu)化工具可實(shí)現(xiàn)優(yōu)化的模型精度和處理效率l便捷的編譯流程

2023-09-18 21:54:33

Vitis AI 概述

AMD Vitis? AI 開(kāi)發(fā)環(huán)境可在 AMD 硬件平臺(tái)上加速 AI 推斷,包括邊緣器件和 AMD Versal? 加速器卡。這一綜合性框架包括最優(yōu)化 IP 核、多用途

2023-10-16 04:22:23

22.04 + Vitis AI v3.0

root@kria:~# uname -a

Linux kria 5.15.0-1020-xilinx-zynqmp #22-Ubuntu SMP Fri Feb

2023-09-10 13:15:24

推斷開(kāi)發(fā)平臺(tái),它可以幫助開(kāi)發(fā)者在賽靈思的 FPGA 和自適應(yīng) SoC 上實(shí)現(xiàn)高效的 AI 應(yīng)用部署。它是一個(gè)強(qiáng)大而靈活的 AI 開(kāi)發(fā)平臺(tái),它可以讓您充分利用賽靈思硬件平臺(tái)的優(yōu)勢(shì),實(shí)現(xiàn)高性能、低功耗

2023-10-14 15:34:26

本文將介紹如何使用Vitis-AI加速YOLOX模型實(shí)現(xiàn)視頻中的目標(biāo)檢測(cè),并對(duì)相關(guān)源碼進(jìn)行解讀。由于演示的示例程序源碼是Vitis-AI開(kāi)源項(xiàng)目提供的,本文演示之前會(huì)介紹所需要的準(zhǔn)備工作。演示之后

2023-10-06 23:32:47

~

$ git clone https://github.com/Xilinx/Vitis-AI

Git下載不成功,可能就是網(wǎng)絡(luò)不太好,在等等在嘗試。

1.2、安裝交叉編譯系統(tǒng)環(huán)境。

$ cd

2023-09-26 16:22:43

一、開(kāi)發(fā)環(huán)境

1.1、使用DPU鏡像系統(tǒng)

https://china.xilinx.com/member/forms/download/design-license-xef.html

2023-09-26 16:43:01

一、開(kāi)發(fā)環(huán)境

1.1、使用DPU鏡像系統(tǒng)

https://china.xilinx.com/member/forms/download/design-license-xef.html

2023-09-26 16:28:10

一、基礎(chǔ)知識(shí)

(一)Vitis? AI開(kāi)發(fā)環(huán)境

Vitis? AI開(kāi)發(fā)環(huán)境可在賽靈思硬件平臺(tái)上加速 AI 推斷,包括邊緣器件和 Alveo? 加速器卡。此環(huán)境由經(jīng)過(guò)最優(yōu)化的 IP 核、工具、庫(kù)、模型

2023-09-27 23:21:32

/ug1354-xilinx-ai-sdk/%E4%B8%8B%E8%BD%BD-Vitis-AI-Library

在安裝->設(shè)置目標(biāo)->步驟1:安裝開(kāi)發(fā)板鏡像

開(kāi)始下載鏡像

進(jìn)入到

2023-08-27 23:35:48

、深度學(xué)習(xí)推斷處理器(DPU)運(yùn)行時(shí)設(shè)計(jì)介紹3、如何加速優(yōu)化,提高系統(tǒng)并行執(zhí)行效率1、AI芯片中的操作系統(tǒng)管理原則2、操作系統(tǒng)運(yùn)行時(shí)設(shè)計(jì)準(zhǔn)則3、多核多線程加速計(jì)算效率方法主講老師:陳小柏,男,中山大學(xué)

2019-11-07 14:18:45

慮公開(kāi)。實(shí)際上本次開(kāi)發(fā)也是一步步按照xilinx官網(wǎng)和網(wǎng)上的資料進(jìn)行設(shè)計(jì)和實(shí)現(xiàn),本來(lái)米爾科技有一套比較完備的實(shí)現(xiàn)方案,并且穩(wěn)定性,開(kāi)發(fā)周期都更加優(yōu)秀,但是自己的還是更適合自己,此次也比較遺憾,項(xiàng)目比較

2021-01-10 14:39:17

1 Vitis AiVitis? AI 開(kāi)發(fā)環(huán)境是 Xilinx 的開(kāi)發(fā)平臺(tái),適用于在 Xilinx 硬件平臺(tái)(包括邊緣器件和 Alveo 卡)上進(jìn)行人工智能推斷。它由優(yōu)化的 IP、工具、庫(kù)、模型

2020-12-03 19:22:13

為什么需要嵌入式AI?嵌入式AI還有瓶頸半導(dǎo)體廠商的新商機(jī)

2021-01-22 06:14:40

要使用FPGA實(shí)現(xiàn)150M的光纖通訊,使用XILINX XAPP244的串行數(shù)據(jù)恢復(fù)功能感覺(jué)有些麻煩。使用XILINX的ROCKET I/O 實(shí)現(xiàn)150M的光纖通信合適/可行嗎?

2013-03-26 16:06:30

出現(xiàn)網(wǎng)絡(luò)和數(shù)據(jù)存儲(chǔ)協(xié)議處理的瓶頸或延遲。VCK190 評(píng)估套件和 Design Gateway 的網(wǎng)絡(luò)和存儲(chǔ) IP 解決方案可在 Xilinx 的 Versal AI Core 器件上以盡可能低的 FPGA 資源使用量和極高的能效在 AI 應(yīng)用中實(shí)現(xiàn)最佳性能。

2022-11-25 16:29:20

千芯科技推出了針對(duì)芯來(lái)RISC-V平臺(tái)的AI部署工具包(tinyAI SDK),使用戶可以基于該先進(jìn)技術(shù)快速部署基于芯來(lái)RISC-V內(nèi)核的AIoT應(yīng)用。在芯來(lái)UX600上,實(shí)測(cè)的AI應(yīng)用實(shí)現(xiàn)

2020-11-21 10:08:17

嘗試在 i.MX93 EVKCM 上的 EthosU NPU 上推斷 AI 模型時(shí)遇到錯(cuò)誤。

使用的 BSP:Linux imx93evk 6.1.1+g29549c7073bf

首先,我從

2023-06-05 11:36:22

如何實(shí)現(xiàn)Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)?

2021-12-23 08:53:58

如何實(shí)現(xiàn)瘋殼AI開(kāi)源無(wú)人機(jī)遙控整機(jī)代碼走讀/編譯與燒寫?

2021-12-20 06:28:42

供CC16CLE.vhd和CB16CLE.vhd。它們是完全相同的文件,只是名稱不同,維護(hù)評(píng)論也很差。現(xiàn)在我遇到的問(wèn)題是,如果Xilinx提供CC16CLE.vhd來(lái)推斷你的設(shè)計(jì)中的這個(gè)計(jì)數(shù)器,他們還應(yīng)該包括實(shí)現(xiàn)這個(gè)

2019-07-08 08:24:31

擴(kuò)展包x-cube-ai能實(shí)現(xiàn)SVM支持向量機(jī)嘛

2024-03-22 07:26:57

AI實(shí)現(xiàn)的特點(diǎn)有哪些?AI芯片設(shè)計(jì)和開(kāi)發(fā)面臨哪些挑戰(zhàn)?

2021-11-02 09:19:08

將 TensorFlow* 模型轉(zhuǎn)換為 IR。

無(wú)法確定使用 IR 實(shí)現(xiàn)OpenVINO?運(yùn)行時(shí)推斷管道的步驟。

2023-08-15 06:23:04

求基于NI采集實(shí)現(xiàn)AI輸入連續(xù)采集,采集任務(wù)執(zhí)行時(shí)間需要硬件定時(shí)來(lái)實(shí)現(xiàn)的范例,有做過(guò)的請(qǐng)指導(dǎo)一下,謝謝!

2016-04-14 17:04:05

` 9月25日,米爾官方發(fā)布,其MYD-CZU3EG開(kāi)發(fā)板在原產(chǎn)品的基礎(chǔ)上搭載了Xilinx深度學(xué)習(xí)處理單元DPU,該部分新功能的增加可以極大的提升產(chǎn)品數(shù)據(jù)處理與運(yùn)行效率,為AI應(yīng)用落地提供完整

2020-09-27 12:10:02

將AI推向邊緣的影響通過(guò)在邊緣運(yùn)行ML模型可以使哪些具體的AI項(xiàng)目更容易運(yùn)行?

2021-02-23 06:21:10

主板用STM32H7B3I-DK然后配一個(gè)普通的攝像頭,可以實(shí)現(xiàn)視覺(jué)AI嗎

2023-08-08 08:09:50

://www.xilinx.com/support/answers/54778.html下載了示例項(xiàng)目我得到了同樣的結(jié)果...... 0 BRAM。這很奇怪也很有趣,沒(méi)有示例代碼可以推斷出BRAM ....附件是示例項(xiàng)目。

2020-05-25 16:08:34

自動(dòng)駕駛車輛中的AI分析車輛中的AI應(yīng)用

2021-03-09 07:53:23

通過(guò)運(yùn)行兩個(gè)進(jìn)程來(lái)推斷同一個(gè)模型,推斷時(shí)間翻倍。

使用OpenVINO?推斷模型。

運(yùn)行單個(gè)過(guò)程時(shí),推斷時(shí)間約為 300ms。

使用兩個(gè)進(jìn)程時(shí),兩個(gè)進(jìn)程的推理時(shí)間將變?yōu)?600ms。

2023-08-15 07:04:47

針對(duì)主要輸出可直接測(cè)量的時(shí)滯系統(tǒng),提出一種模糊反饋推斷控制器。該控制器是在典型推斷控制的基礎(chǔ)上進(jìn)行簡(jiǎn)化和改進(jìn),并用模糊邏輯和推理來(lái)自適應(yīng)地調(diào)節(jié)控制器的濾波器時(shí)

2010-01-16 17:11:28 8

8 提出橡膠密煉機(jī)的一種基于神經(jīng)網(wǎng)絡(luò)軟測(cè)量的推斷控制系統(tǒng),針對(duì)橡膠密煉機(jī)混煉膠的質(zhì)量指標(biāo)需要比較精確估計(jì)的一類軟測(cè)量建模問(wèn)題,研究了適用于%&’( 軟測(cè)量模型的一種

2010-10-07 15:30:08 44

44 通過(guò)Xilinx Spartan-6 FPGA 的Multiboot特性,允許用戶一次將多個(gè)配置文件下載入Flash中,根據(jù)不同時(shí)刻的需求,在不掉電重啟的情況下,從中選擇一個(gè)來(lái)重配置FPGA,實(shí)現(xiàn)不同功能,提高器件利用率,增加

2012-03-22 17:18:56 65

65 在Xilinx FPGA上快速實(shí)現(xiàn) JESD204B

2016-01-04 18:03:06 0

0 Xilinx FPGA工程例子源碼:Xilinx TCP_IP協(xié)議實(shí)現(xiàn)

2016-06-07 14:54:57 31

31 采用Xilinx_Zynq_SoC實(shí)現(xiàn)眼動(dòng)追蹤技術(shù),感興趣的小伙伴們可以瞧一瞧。

2016-10-26 15:55:29 0

0 ,這兩個(gè)寄存器可以被放置在同一個(gè)Slice里面。在VIVADO和ISE下面都有選項(xiàng)來(lái)幫助大家自動(dòng)實(shí)現(xiàn)該功能。大家在做設(shè)計(jì)的時(shí)候可以選用。 做設(shè)計(jì)的時(shí)候有些原則還應(yīng)該注意: 在控制信號(hào)的規(guī)劃的時(shí)候,XILINX的原語(yǔ)和IP的例化可能增加額外的控制信號(hào)到用

2017-02-08 06:35:36 146

146

(Xilinx)FPGA中LVDS差分高速傳輸?shù)?b class="flag-6" style="color: red">實(shí)現(xiàn)

2017-03-01 13:12:04 64

64 xilinx 約束實(shí)現(xiàn)

2017-03-01 13:12:47 15

15 推斷數(shù)據(jù)間存在的因果關(guān)系是很多科學(xué)領(lǐng)域中的一個(gè)基礎(chǔ)問(wèn)題,然而現(xiàn)在暫時(shí)還沒(méi)有快速有效的方法對(duì)缺失數(shù)據(jù)進(jìn)行因果推斷。為此,提出一種基于加性噪聲模型下適應(yīng)缺失數(shù)據(jù)的因果推斷算法。該算法是基于加性噪聲模型

2018-01-14 16:06:38 0

0 FPGA仿真篇-使用腳本命令來(lái)加速仿真二 基于FPGA的HDMI高清顯示借口驅(qū)動(dòng) 基于FPGA灰度圖像高斯濾波算法的實(shí)現(xiàn) FPGA為什么比CPU和GPU快 基于Xilinx FPGA的視頻圖像采集

2018-02-20 20:44:00 1256

1256

隨著智能安全、機(jī)器人或無(wú)人駕駛汽車等應(yīng)用越來(lái)越依靠嵌入式人工智能技術(shù)來(lái)提高性能,交付全新的用戶體驗(yàn),推斷引擎必須滿足嚴(yán)格定義的推斷精度,還受限于總線寬度,而且存儲(chǔ)器難以為最佳速度、效率和芯片面積進(jìn)行調(diào)整優(yōu)化。

2018-10-22 16:03:54 3262

3262 在此Xilinx研究實(shí)驗(yàn)室演示中,解釋了單源SYCL C ++示例以及生成在Xilinx FPGA上運(yùn)行的硬件實(shí)現(xiàn)的方法。

2018-11-20 06:30:00 2918

2918 在本演示中,Intelliprop演示了在Xilinx Zynq UltraScale + MPSoC中實(shí)現(xiàn)的NVMe主機(jī)加速器。

2018-11-26 06:18:00 5658

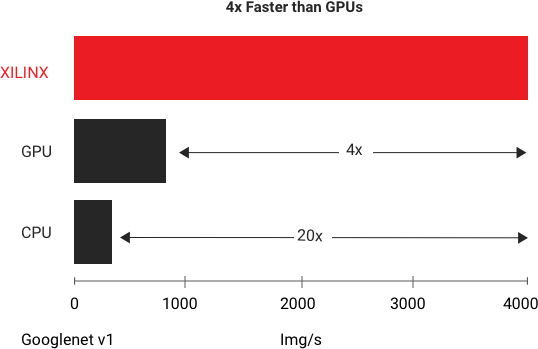

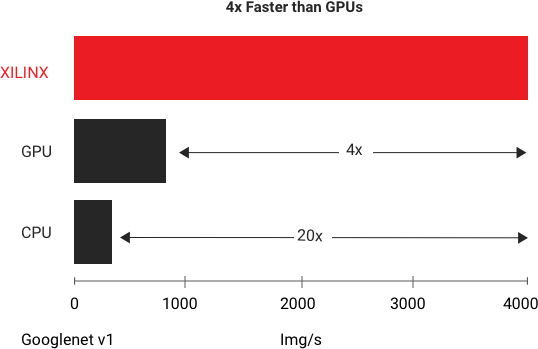

5658 在數(shù)據(jù)中心 AI 平臺(tái)上,對(duì)于低時(shí)延 AI 推斷,賽靈思能以最低時(shí)延的條件下提供最高吞吐量,在 GoogleNet V1 上進(jìn)行的標(biāo)準(zhǔn)基準(zhǔn)測(cè)試當(dāng)中,賽靈思 Alveo U250 可為實(shí)時(shí)推斷提供比現(xiàn)有最快的 GPU 多出 4 倍的吞吐量。

2019-03-09 10:52:40 1233

1233

在數(shù)據(jù)中心 AI 平臺(tái)上,對(duì)于低時(shí)延 AI 推斷,賽靈思能以最低時(shí)延的條件下提供最高吞吐量,在 GoogleNet V1 上進(jìn)行的標(biāo)準(zhǔn)基準(zhǔn)測(cè)試當(dāng)中,賽靈思 Alveo U250 可為實(shí)時(shí)推斷提供比現(xiàn)有最快的 GPU 多出 4 倍的吞吐量。

2019-03-11 16:13:31 3408

3408 在數(shù)據(jù)中心 AI 平臺(tái)上,對(duì)于低時(shí)延 AI 推斷,賽靈思能以最低時(shí)延的條件下提供最高吞吐量。

2019-07-25 17:13:12 1968

1968

Zebra 可消除深度學(xué)習(xí)推斷中具有挑戰(zhàn)性的編程及 FPGA 任務(wù)。Zebra 可輕松部署和適應(yīng)廣泛的神經(jīng)網(wǎng)絡(luò)及框架。

2019-07-21 10:59:09 893

893

2019年12月2日,中國(guó),北京(2019 年賽靈思中國(guó)開(kāi)發(fā)者論壇) —— 自適應(yīng)和智能計(jì)算的全球領(lǐng)先企業(yè)賽靈思公司今天宣布其 人工智能推斷開(kāi)發(fā)軟件平臺(tái)Vitis AI即日起開(kāi)放免費(fèi)下載,更多開(kāi)發(fā)者將體驗(yàn)并受益于賽靈思所提供的從邊緣到云的人工智能和深度學(xué)習(xí)推斷加速度。

2019-12-04 13:43:55 1920

1920 Eyeris車內(nèi)傳感器融合AI整合了圖像、雷達(dá)和熱成像傳感器技術(shù),并在合作伙伴的最新AI處理器上對(duì)車內(nèi)傳感器融合AI進(jìn)行推斷,準(zhǔn)確獲取對(duì)車內(nèi)場(chǎng)景的理解,涵蓋監(jiān)控駕駛員和乘員監(jiān)控、檢測(cè)物體、對(duì)表面進(jìn)行分類等,目的是提升智能以控制安全性和舒適性。

2020-07-16 17:33:55 701

701 有了世界領(lǐng)先的模型壓縮技術(shù),我們可以在對(duì)精度影響極小的情況下,將模型的復(fù)雜性降低 5 至 50 倍。深度壓縮可將您的 AI 推斷性能提升到一個(gè)新的層次。

2020-08-03 16:40:35 2552

2552

在熟悉的更高層次框架中進(jìn)行開(kāi)發(fā) 不斷發(fā)展的硬件加速合作伙伴庫(kù)和預(yù)建應(yīng)用生態(tài)系統(tǒng) 重要組件 Vitis AI 開(kāi)發(fā)環(huán)境 一個(gè)專門的開(kāi)發(fā)環(huán)境,用于在 Xilinx 嵌入式平臺(tái)、Alveo 加速卡或云端

2020-11-24 13:45:17 2947

2947 Victor Peng在中國(guó)參加媒體會(huì)甚至表示,如果你在一個(gè)行業(yè)內(nèi)達(dá)到了一種高度,你就有資格玩下一關(guān)的游戲。現(xiàn)在Xilinx的ACAP已經(jīng)上了一個(gè)新臺(tái)階,接下來(lái)我們要和英偉達(dá)、英特爾的處理器展開(kāi)新競(jìng)爭(zhēng)。

2020-09-26 11:49:16 2263

2263 神經(jīng)網(wǎng)絡(luò)推斷的實(shí)驗(yàn)框架的全新再實(shí)現(xiàn),而且它現(xiàn)在仍是賽靈思研究實(shí)驗(yàn)室 (Xilinx Research Lab) 的測(cè)試版。然而, 雖然還是測(cè)試版,它已經(jīng)發(fā)布了 v0.4b(測(cè)試版),并且自從在 GitHub 上開(kāi)源以來(lái),受到了廣泛關(guān)注。 2020 年 5 月,賽靈思研究實(shí)驗(yàn)室的論文《FINN-R:快速探

2020-10-17 12:05:48 2521

2521 端到端的軟硬件協(xié)同優(yōu)化,在Xilinx ZU+ MPSoC平臺(tái)上實(shí)時(shí)地運(yùn)行業(yè)界領(lǐng)先的PointPillars模型,實(shí)現(xiàn)高精度的多類別3D目標(biāo)檢測(cè)。 Vitis AI 開(kāi)發(fā)環(huán)境是 Xilinx 的開(kāi)發(fā)平臺(tái),適用于在 Xilinx 硬件平臺(tái)(包括邊緣器件和 Alveo 卡)上進(jìn)行人工智能推斷。它由優(yōu)化的 IP、

2020-11-04 11:22:00 3541

3541 ,有機(jī)遇就會(huì)有挑戰(zhàn)。AI 推斷作為采用經(jīng)訓(xùn)練的機(jī)器學(xué)習(xí)算法開(kāi)展預(yù)測(cè)的過(guò)程,無(wú)論是部署在云端、邊緣還是終端,都要求在嚴(yán)格的功耗預(yù)算下提供優(yōu)異的處理性能。普遍的看法認(rèn)為,僅憑 CPU 難以滿足這一要求,需要某種形式的計(jì)算加速才能更高效地處理 AI 推

2020-11-05 10:30:17 1449

1449 從邊緣到云的最佳人工智能推斷 Vitis AI開(kāi)發(fā)環(huán)境賽靈思為人工智能推理而打造的專用開(kāi)發(fā)平臺(tái),適用于在 Xilinx 硬件平臺(tái)(包括邊緣器件和 Alveo 卡)上進(jìn)行人工智能推斷。它由優(yōu)化的 IP

2020-12-29 11:18:24 2594

2594 本文檔的主要內(nèi)容詳細(xì)介紹的是如何使用Xilinx的FPGA對(duì)高速PCB信號(hào)實(shí)現(xiàn)優(yōu)化設(shè)計(jì)。

2021-01-13 17:00:59 25

25 Versal AI Core 系列提供了 Versal 產(chǎn)品組合中的最高算力和最低時(shí)延,借助其 AI 引擎實(shí)現(xiàn)了突破性的 AI 推斷吞吐量和性能。

2021-04-28 15:16:26 3630

3630 隨著第三次人工智能浪潮的到來(lái),AI正以前所未有的速度覆蓋生產(chǎn)和管理等領(lǐng)域,市場(chǎng)對(duì)AI推斷的效率與易用性都提出了更高的要求。賽靈思通過(guò)?Vitis?AI和自適應(yīng)計(jì)算加速平臺(tái),充分發(fā)掘AI 加速潛能

2021-05-17 10:38:07 1911

1911

)。如何從觀察獲得的數(shù)據(jù)中發(fā)現(xiàn)不同因素之間的因果關(guān)系則是統(tǒng)計(jì)學(xué)、機(jī)器學(xué)習(xí)和人工智能領(lǐng)域具有挑戰(zhàn)性的重要研究問(wèn)題---統(tǒng)計(jì)推斷。 本次Fudan DISC實(shí)驗(yàn)室將分享EMNLP 2020中有關(guān)因果推斷的3篇論文,介紹在不同任務(wù)下因果推斷方法的應(yīng)用。 文章概覽 基于因果推

2021-05-19 15:59:26 4464

4464

平滑性得以增強(qiáng)并采用變分推斷方法獲得聚類標(biāo)簽的收斂解析解,提岀一種基于折棍變分貝葉斯推斷的圖像分割算法,實(shí)現(xiàn)了對(duì)像素聚類標(biāo)簽和分割數(shù)目的同步自適應(yīng)學(xué)習(xí),避免了傳統(tǒng)方法中因引入空間相關(guān)性約束而出現(xiàn)的計(jì)算復(fù)雜問(wèn)題。基于Berkeley BSD5σ0圖像

2021-06-04 15:27:33 3

3 貿(mào)澤電子 (Mouser Electronics) 即日起備貨Xilinx的Kria? KV260視覺(jué)AI入門套件。

2021-06-28 14:45:27 2275

2275

Vitis AI 1.4 賽靈思 Vitis AI 是一款功能強(qiáng)大的機(jī)器學(xué)習(xí)開(kāi)發(fā)平臺(tái),用于在賽靈思自適應(yīng)計(jì)算平臺(tái)上實(shí)現(xiàn) AI 推斷加速。最新發(fā)布的 Vitis AI 1.4 版本為用戶提供了完整

2021-08-09 10:54:33 1435

1435 深度學(xué)習(xí)是推動(dòng)當(dāng)前人工智能大趨勢(shì)的關(guān)鍵技術(shù)。在 MATLAB 中可以實(shí)現(xiàn)深度學(xué)習(xí)的數(shù)據(jù)準(zhǔn)備、網(wǎng)絡(luò)設(shè)計(jì)、訓(xùn)練和部署全流程開(kāi)發(fā)和應(yīng)用。聯(lián)合高性能 NVIDIA GPU 加快深度神經(jīng)網(wǎng)絡(luò)訓(xùn)練和推斷。

2022-02-18 13:31:44 1714

1714 IEEE1588/PTP 協(xié)議是實(shí)時(shí)工業(yè)軟件的一個(gè)重要的協(xié)議,本博文討論該協(xié)議在Xilinx Zynq 系統(tǒng)·上如何實(shí)現(xiàn)IEEE1588 協(xié)議。

2022-09-21 14:28:51 2888

2888 Vitis AI Library 是一組高層次庫(kù)和 API,專為利用深度學(xué)習(xí)處理單元 (DPU) 來(lái)高效執(zhí)行 AI 推斷而構(gòu)建。

2022-10-10 10:26:47 1354

1354 本篇主要介紹Xilinx FPGA的電源設(shè)計(jì),主要包括電源種類、電壓要求、功耗需求,上下電時(shí)序要求,常見(jiàn)的電源實(shí)現(xiàn)方案等。

2022-10-17 17:43:39 3073

3073 電子發(fā)燒友網(wǎng)站提供《使用Xilinx Kria KV260進(jìn)行AI火災(zāi)探測(cè).zip》資料免費(fèi)下載

2022-10-27 10:12:30 5

5 使用always_ff和在靈敏度列表中指定一個(gè)時(shí)鐘邊沿并不意味著過(guò)程中的所有邏輯都是時(shí)序邏輯。綜合編譯器將推斷出每個(gè)被非阻塞賦值的變量的觸發(fā)器。阻塞賦值也可能推斷出觸發(fā)器,這取決于賦值語(yǔ)句相對(duì)于程序中其他賦值和操作的順序和上下文。

2023-02-20 10:38:06 442

442 電子發(fā)燒友網(wǎng)站提供《Xilinx KV260 Vitis-AI 1.4人臉檢測(cè).zip》資料免費(fèi)下載

2023-06-14 10:34:43 0

0 Xilinx?的?Versal AI Core?系列器件旨在解決有關(guān) AI 推理的最大而獨(dú)特的難題

2023-07-07 14:15:13 531

531

OFDM中調(diào)制使用IFFT,解調(diào)使用IFFT,在OFDM實(shí)現(xiàn)系統(tǒng)中,F(xiàn)FT和IFFT時(shí)必備的關(guān)鍵模塊。在使用Xilinx的7系列FPGA(KC705)實(shí)現(xiàn)OFDM系統(tǒng)時(shí),有以下幾種選擇。

2023-07-10 10:50:52 605

605

靜態(tài)類型推斷是維護(hù)動(dòng)態(tài)類型語(yǔ)言程序安全的重要手段之一。然而,另一種編程語(yǔ)言實(shí)現(xiàn)的外部函數(shù)往往不在宿主語(yǔ)言的類型推斷范圍內(nèi)。

2023-07-14 17:42:08 507

507

電子發(fā)燒友網(wǎng)站提供《面向邊緣的集成AI訓(xùn)練和推斷解決方案.pdf》資料免費(fèi)下載

2023-09-13 10:25:36 0

0 電子發(fā)燒友網(wǎng)站提供《Xilinx AI SDK編程指南.pdf》資料免費(fèi)下載

2023-09-15 11:15:34 0

0 電子發(fā)燒友網(wǎng)站提供《AI和Xilinx如何加速暗物質(zhì)搜索.pdf》資料免費(fèi)下載

2023-09-15 14:19:59 1

1 電子發(fā)燒友網(wǎng)站提供《Xilinx AI SDK用戶指南.pdf》資料免費(fèi)下載

2023-09-15 14:22:34 0

0 電子發(fā)燒友網(wǎng)站提供《用賽靈思FPGA加速機(jī)器學(xué)習(xí)推斷.pdf》資料免費(fèi)下載

2023-09-15 15:02:17 1

1

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論