資料介紹

前幾天和同事聊天,他說他上初中的兒子做出了一道很難的數(shù)學(xué)題,想考考我們這些大學(xué)生看能不能做得出來?

題目很簡(jiǎn)單:

大家先嘗試做一下?我沒想出怎么算的,只是用排除法確定了a和b的范圍,然后再逐個(gè)嘗試。

1.對(duì)4361進(jìn)行開方計(jì)算,得到結(jié)果最大為66,則a,b的值均小于等于66。

2.對(duì)4361/2進(jìn)行開方計(jì)算,則得到結(jié)果為46,則a,b兩者,一個(gè)是1-46,一個(gè)是46-66之間的數(shù)。

3.由平方和4361末尾為1,再根據(jù)整數(shù)平方和的幾種可能,計(jì)算出僅有0+1和5+6這兩種可能,而且平方之后的個(gè)位數(shù)為0/1/5/6,這樣就進(jìn)一步縮小了范圍,通過多次計(jì)算嘗試可以得出結(jié)果。

不過我懶得算了,就簡(jiǎn)單寫了個(gè)C語言程序,計(jì)算出了結(jié)果:

#include?#include? #include? int?main(void) { ????int?num;????? ????int?a,?b,?n; ????int?result; ????int?sqr; ????printf("please?enter?a?number:");//4361 ????scanf("%d",?&num); ????printf("input?num:?%d\n",?num); ????sqr?=?sqrt(num); ????for(a?=?1;?a?<=?sqr;?a++)????????//可以設(shè)置1-46 ????{ ????????for(b?=?1;?b?<=?sqr;?b++)????//可以設(shè)置46-66 ????????{ ????????????result?=?pow(a,?2)?+?pow(b,?2); ????????????if(result?==?num) ????????????{ ????????????????printf("a?=?%2d,?b?=?%2d,?a?+?b?=?%d\n",?a,?b,?a+b); ????????????????n++; ????????????} ????????} ????} ????if(n?==?0) ????????printf("There?is?no?answer!\n"); ????return?0; }

其實(shí)可以設(shè)置一個(gè)數(shù)的循環(huán)范圍是:1-46,一個(gè)數(shù)的循環(huán)范圍是46-66,這樣會(huì)減少循環(huán)次數(shù)。

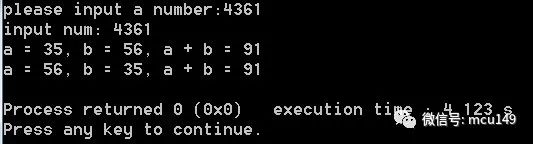

運(yùn)行結(jié)果:

運(yùn)行結(jié)果

運(yùn)行結(jié)果

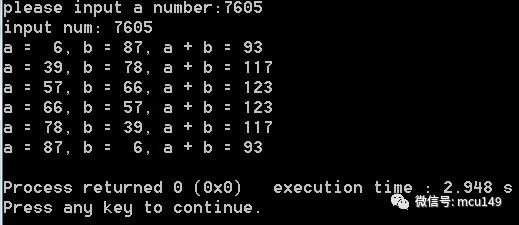

而且這種方式還適用于解的個(gè)數(shù)不唯一的情況,比如7605:

運(yùn)行結(jié)果

運(yùn)行結(jié)果

作為一個(gè)野生FPGA開發(fā)者,我在想能不能用FPGA的編程思想來實(shí)現(xiàn)呢?也就是如何用Verilog來實(shí)現(xiàn)兩個(gè)循環(huán)的嵌套呢?抄起鍵盤就是干!

抄起鍵盤就是干

抄起鍵盤就是干

verilog源文件fpga_math.v:

module?fpga_math( ????//inputs ????input?clk, ????input?rst_n, ????//outputs ????output?reg?[13:0]?a,?b, ????output?reg?[14:0]?result, ????output?ok ); parameter?SUM?=?4361; parameter?SQR?=?67;???????//sqrt(SUM); reg?[13:0]?tmp_a; reg?[13:0]?tmp_b; reg?flag; assign?ok?=?(tmp_a*tmp_a?+?tmp_b*tmp_b?==?SUM); always?@?(posedge?clk) begin ????if(!rst_n) ????????tmp_b?<=?0; ????else?if(tmp_b?==?SQR) ????????tmp_b?<=?0; ????else?if(tmp_a?!=?SQR) ????????tmp_b?<=?tmp_b?+?1; end always?@?(posedge?clk) begin ????if(!rst_n) ????????flag?<=?0; ????else?if(tmp_b?==?SQR) ????????flag?<=?1; ????else? ????????flag?<=?0; end always?@?(posedge?clk) begin ????if(!rst_n) ????????tmp_a?<=?0; ????else?if((tmp_a?!=?SQR)?&?flag) ????????tmp_a?<=?tmp_a?+?1; end always?@?(posedge?clk) begin ????if(!rst_n) ????begin ????????a?<=?0; ????????b?<=?0; ????????result?<=?0; ????end ????else?if(ok) ????begin ????????a?<=?tmp_a; ????????b?<=?tmp_b; ????????result?=?tmp_a?+?tmp_b; ????end end endmodule

為了驗(yàn)證這個(gè)模塊的正確性,我們需要對(duì)這個(gè)模塊進(jìn)行仿真,即給一個(gè)激勵(lì)輸入信號(hào),看輸出是否正確。

新建testbench文件fpga_math_tb.v:

`timescale?1ns/100ps module?fpga_math_tb; parameter?SUM?=?4361; parameter?SQR?=?67;?????//sqrt(4361) parameter?SYSCLK_PERIOD?=?10;//?100MHZ wire?[13:0]?a,?b; wire?[14:0]?result; reg?SYSCLK; reg?NSYSRESET; initial begin ????SYSCLK?=?1'b0; ????NSYSRESET?=?1'b0; ????#(SYSCLK_PERIOD?*?10?) ????????NSYSRESET?=?1'b1; ????#(SYSCLK_PERIOD?*?(SQR*SQR+500)?) ????????$stop; end /*generate?clock*/ always?@(SYSCLK) ????#(SYSCLK_PERIOD?/?2.0)?SYSCLK?<=?!SYSCLK;??????? /*instance?module*/ fpga_math?#( ????.SUM(SUM), ????.SQR(SQR) )fpga_math_0( ????//inputs ????.clk(SYSCLK), ????.rst_n(NSYSRESET), ????//outputs ????.a(a), ????.b(b), ????.result(result), ????.ok(ok) ); endmodule

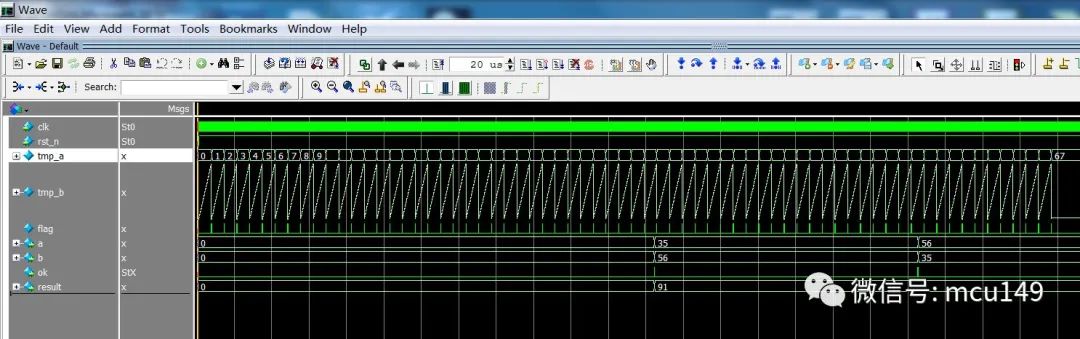

ModelSim仿真波形:

仿真波形

仿真波形

仿真工具除了使用各大FPGA廠商IDE帶的ModelSim等,也可以使用小巧開源的全平臺(tái)仿真工具:iverilog+gtkwave,使用方法可以參考:

如果使用iverilog進(jìn)行仿真,需要在TB文件中添加以下幾行語句:

/*iverilog?*/

initial

begin????????????

????$dumpfile("wave.vcd");????????//生成的vcd文件名稱

????$dumpvars(0,?fpga_math_tb);???//tb模塊名稱

end

/*iverilog?*

首先對(duì)Verilog源文件進(jìn)行編譯,檢查是否有語法錯(cuò)誤,這會(huì)在當(dāng)前目錄生成wave目標(biāo)文件:

iverilog?-o?wave?*.v

然后通過vvp指令,產(chǎn)生仿真的wave.vcd波形文件:

vvp?-n?wave?-lxt2

使用gtkwave打開波形文件:

gtkwave?wave.vcd

當(dāng)然以上命令也可以寫成批處理文件:

echo?"開始編譯" iverilog?-o?wave?*.v echo?"編譯完成" echo?"生成波形文件" vvp?-n?wave?-lxt2 echo?"打開波形文件" gtkwave?wave.vcd

以文本方式存儲(chǔ)為build.bat文件即可,雙擊即可自動(dòng)完成編譯、生成波形文件、打開波形文件操作。

仿真波形:

仿真波形可以看出,和使用ModelSim仿真是一樣的結(jié)果。

總結(jié)

從仿真波形圖中,可以得到計(jì)算的結(jié)果,a+b的值為91,如果要在真實(shí)的FPGA芯片硬件上實(shí)現(xiàn),還需要添加其他功能模塊,把結(jié)果通過串口輸出,或者在數(shù)碼管等顯示屏上進(jìn)行顯示,這里只是簡(jiǎn)單介紹使用FPGA計(jì)算方法的實(shí)現(xiàn)。作為純數(shù)字電路的FPGA,實(shí)現(xiàn)平方根是比較復(fù)雜的,這里采用直接人為輸入平方根結(jié)果的方式,而不是像C語言那樣調(diào)用sqrt函數(shù)自動(dòng)計(jì)算平方根。FPGA中不僅有觸發(fā)器和查找表,而且還有乘法器、除法器等硬核IP,所以在涉及到乘除法、平方根運(yùn)算時(shí),不要直接使用*/等運(yùn)算符,而是要使用FPGA自帶的IP核,這樣就不會(huì)占用大量的邏輯資源,像Xilinx的基于Cordic算法的Cordic IP核,不僅能實(shí)現(xiàn)平方根計(jì)算,而且還有sin/cos/tan/arctan等三角函數(shù)。

- 單片機(jī)C語言和匯編語言混合編程實(shí)例詳解 227次下載

- MATLAB語言與C語言的區(qū)別資料下載

- 八位串行和并行轉(zhuǎn)換電路的仿真電路圖免費(fèi)下載 22次下載

- 使用單片機(jī)實(shí)現(xiàn)鍵盤掃描顯示的C語言和資料免費(fèi)下載 2次下載

- 使用C語言和C++編寫俄羅斯方塊的資料和源代碼免費(fèi)下載 4次下載

- 出租車計(jì)價(jià)器的C語言程序免費(fèi)下載 22次下載

- 溫度數(shù)碼管的C語言和工程文件免費(fèi)下載 0次下載

- 超聲波測(cè)距串口顯示的C語言和工程文件免費(fèi)下載 16次下載

- 使用單片機(jī)設(shè)計(jì)搶答器的C語言和工程文件免費(fèi)下載 12次下載

- DS1302時(shí)鐘芯片的使用源代碼免費(fèi)下載 17次下載

- 使用51單片機(jī)實(shí)現(xiàn)DHT11溫濕度檢測(cè)的代碼程序免費(fèi)下載 138次下載

- 使用51單片機(jī)C語言和匯編兩種方式實(shí)現(xiàn)設(shè)計(jì)時(shí)鐘的程序免費(fèi)下載

- MATLAB 64位C語言和C++編譯器應(yīng)用程序免費(fèi)下載 4次下載

- C語言和C++編程的一些思考資料說明

- 我的計(jì)算器C語言程序免費(fèi)下載 16次下載

- Verilog與VHDL的比較 Verilog HDL編程技巧 259次閱讀

- 串口屏支持哪些編程語言和開發(fā)環(huán)境? 294次閱讀

- C語言和C++中結(jié)構(gòu)體的區(qū)別 314次閱讀

- PLC編程語言和C語言的區(qū)別 3090次閱讀

- fpga是用c語言還是verilog 2106次閱讀

- plc編程語言與c語言的聯(lián)系 c語言和PLC有什么區(qū)別 4302次閱讀

- vb語言和c++語言的區(qū)別 2434次閱讀

- C語言和C++中那些不同的地方 987次閱讀

- C語言和C++的特點(diǎn)與用法詳細(xì)說明 4445次閱讀

- 詳談C語言和C++的區(qū)別和聯(lián)系 5830次閱讀

- C語言和指針之間的關(guān)系分析 1169次閱讀

- 計(jì)算機(jī)的機(jī)器語言和匯編語言與高級(jí)語言的詳細(xì)資料介紹 5893次閱讀

- 高級(jí)語言和匯編語言_機(jī)器語言的區(qū)別 3w次閱讀

- 學(xué)習(xí)開發(fā)環(huán)境和編程語言:匯編語言和C語言的比較 9082次閱讀

- verilog語言與c語言的區(qū)別 1.2w次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費(fèi)下載

- 0.00 MB | 1491次下載 | 免費(fèi)

- 2單片機(jī)典型實(shí)例介紹

- 18.19 MB | 95次下載 | 1 積分

- 3S7-200PLC編程實(shí)例詳細(xì)資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識(shí)別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 5開關(guān)電源原理及各功能電路詳解

- 0.38 MB | 11次下載 | 免費(fèi)

- 6100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 7基于單片機(jī)和 SG3525的程控開關(guān)電源設(shè)計(jì)

- 0.23 MB | 4次下載 | 免費(fèi)

- 8基于AT89C2051/4051單片機(jī)編程器的實(shí)驗(yàn)

- 0.11 MB | 4次下載 | 免費(fèi)

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費(fèi)

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費(fèi)

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費(fèi)

- 4LabView 8.0 專業(yè)版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費(fèi)

- 5555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33562次下載 | 免費(fèi)

- 6接口電路圖大全

- 未知 | 30320次下載 | 免費(fèi)

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費(fèi)

- 8開關(guān)電源設(shè)計(jì)實(shí)例指南

- 未知 | 21539次下載 | 免費(fèi)

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費(fèi)

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537793次下載 | 免費(fèi)

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費(fèi)

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費(fèi)

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費(fèi)

- 6電路仿真軟件multisim 10.0免費(fèi)下載

- 340992 | 191183次下載 | 免費(fèi)

- 7十天學(xué)會(huì)AVR單片機(jī)與C語言視頻教程 下載

- 158M | 183277次下載 | 免費(fèi)

- 8proe5.0野火版下載(中文版免費(fèi)下載)

- 未知 | 138039次下載 | 免費(fèi)

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評(píng)論