完善資料讓更多小伙伴認識你,還能領(lǐng)取20積分哦,立即完善>

標簽 > versal

Versal 產(chǎn)品組合基于 臺積電(TSMC)的 7 nm FinFET 工藝技術(shù),是第一個將軟件可編程性與特定領(lǐng)域硬件加速和靈活應(yīng)變能力相結(jié)合的平臺,這對于跟上當今快速的創(chuàng)新步伐至關(guān)重要。

文章:70個 瀏覽:7710次 帖子:0個

第二代AMD Versal Premium系列器件的主要應(yīng)用

隨著數(shù)據(jù)中心工作負載持續(xù)呈指數(shù)級增長,存儲層也需要同等的性能提升才能跟上步伐。第二代 AMD Versal Premium 系列器件為各種存儲應(yīng)用提供了...

2025-01-15 標簽:amd數(shù)據(jù)中心Versal 158 0

第二代AMD Versal Premium系列產(chǎn)品亮點

第二代 AMD Versal Premium 系列提供了全新水平的存儲器和數(shù)據(jù)帶寬,具備 CXL 3.1、PCIe Gen6 和 DDR5/LPDDR5...

如何通過PMC_GPIO喚醒AMD Versal? Adaptive SoC Linux系統(tǒng)

在功耗敏感的系統(tǒng)里,我們通常會在系統(tǒng)空閑的時候?qū)⑾到y(tǒng)休眠,然后可以通過一些外設(shè)的輸入來喚醒系統(tǒng),比如 Uart、USB 和 GPIO。AMD Versa...

借助第二代 AMD VERSAL 實現(xiàn)先進醫(yī)療成像

診斷醫(yī)療成像設(shè)備必須能夠產(chǎn)出高質(zhì)量圖像、實現(xiàn)所需的掃描深度,以及顯示實時結(jié)果。設(shè)備中采用的最優(yōu)片上系統(tǒng)( SoC )必須提供所需的應(yīng)用性能、目標幀率并實...

使用 AMD Versal AI 引擎釋放 DSP 計算的潛力

“Versal AI 引擎可以在降低功耗預(yù)算的情況下提高 DSP 計算密度,”高級產(chǎn)品營銷經(jīng)理 Udayan Sinha 表示。這種效率使 Versal...

AMD Vitis Unified Software Platform 2024.2發(fā)布

近日,全新 AMD Vitis Unified Software Platform 2024.2 版本推出。

近日,AMD(超威,納斯達克股票代碼:AMD )今日宣布推出第二代 AMD Versal Premium 系列,這款自適應(yīng) SoC 平臺旨在面向各種工作...

Versal自適應(yīng)SoC讓Combo PON方案高性能、易于使用

通信服務(wù)提供商往往采用無源光網(wǎng) (PON) 為最終用戶帶來高速和低成本的光纖接入。它們通常作為在最后一英里將互聯(lián)網(wǎng)和云連接到家庭和企業(yè)的紐帶。過去幾年里...

2023-05-11 標簽:amdsoc光纖網(wǎng)絡(luò) 992 0

控制內(nèi)核在 AI 引擎陣列中的相對布局,從而提升性能,提高利用率。

Versal ACAP,APU - 跟蹤系統(tǒng)中發(fā)生 ATB 停滯可能引發(fā)處理器死鎖

處理器可使用等待事件 (wait for event, WFE) 或等待中斷 (wait for interrupt, WFI) 機制來進入低功耗狀態(tài)。...

Versal ACAP、APU - DSB 指令后可能會發(fā)生推測性 TLB 填充

Arm 發(fā)行的白皮書 "Cache Speculation Side-channels"用于發(fā)現(xiàn) "Spectre&quo...

Versal ACAP,APU - 由于舊負載檢測到異步外部異常中止,導(dǎo)致新負載誤報同步外部異常中止

在某些條件下,新負載如果復(fù)用舊器件負載的分組標識 (GID),則可能報告同步外部異常中止,原因是錯誤關(guān)聯(lián)舊器件存儲器訪問所檢測到的外部錯誤。器件負載快速...

Versal ACAP PS GEM - GEM 控制器可能在大型發(fā)送卸載配置中觸發(fā)錯誤的 Amba_Error

當在硬件配置中包含“大型發(fā)送卸載 (Large Send Offload)”并在緩沖區(qū)描述符中啟用 LSO 功能時,GEM IP 可能通過中斷狀態(tài)寄存器...

Versal ACAP, RPU - 為調(diào)試寄存器 DBGDSAR 設(shè)置的值錯誤

每個 RPU 處理器都有 1 個 DBGDSAR 寄存器,其中包含其 CoreSight ROM 表的偏移地址。但是,讀取 RPU 的 DBGDSAR ...

Versal ACAP、APU - ELR 錯誤報告序列中加密指令之間的中斷

在 aarch32 模式下,如果執(zhí)行的代碼包含下面的加密指令序列,并且在執(zhí)行第一條加密指令后立即斷言并中斷,ELR 會被記錄為返回地址,產(chǎn)生的錯誤可能會...

Versal ACAP,APU - 當有逐出傳輸事務(wù)處于暫掛狀態(tài)時,外部數(shù)據(jù)嗅探可能導(dǎo)致數(shù)據(jù)損壞

如果 Arm Cortex-A72 處理器配置為向處于 UniqueClean (UC) 狀態(tài)的緩存行發(fā)送逐出傳輸事務(wù),那么 Cortex-A72 處理...

2022-08-05 標簽:APU數(shù)據(jù)損壞Versal 377 0

Vitis 環(huán)境開發(fā)方法論反應(yīng)了 Versal ACAP 系統(tǒng)的異構(gòu)性質(zhì),此類系統(tǒng)通常是由 PS、PL 和 AI 引擎功能組成的。您可使用 Vitis ...

Versal與MPSoC在cache維護數(shù)據(jù)的架構(gòu)上,有一定的相似性。所以在Versal器件里,我們?nèi)匀豢梢允褂蒙鲜鑫臋n [1] 里8.1和8.2的ch...

2022-04-21 標簽:數(shù)據(jù)檢測系統(tǒng)Versal 1133 0

Versal 自適應(yīng)計算加速平臺 (ACAP) 將標量引擎 (Scalar Engine)、自適應(yīng)引擎 (Adaptable Engine) 和智能引擎...

賽靈思Versal自適應(yīng)計算加速平臺助于高效實現(xiàn)設(shè)計目標

隨著AI、大數(shù)據(jù)、云計算等技術(shù)在各行各業(yè)廣泛應(yīng)用,相應(yīng)的設(shè)計結(jié)構(gòu)和設(shè)計內(nèi)容也變得日益復(fù)雜。目前的應(yīng)用開發(fā)速度已無法滿足企業(yè)的需求,如何簡化設(shè)計進程,提高...

換一批

換一批

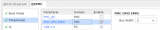

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |