電子發(fā)燒友網(wǎng)站提供《完整的DDR2、DDR3和DDR3L內(nèi)存電源解決方案同步降壓控制器TPS51216數(shù)據(jù)表.pdf》資料免費下載

2024-03-13 13:58:12 0

0 電子發(fā)燒友網(wǎng)站提供《適用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF緩沖基準的TPS51206 2A峰值灌電流/拉電流DDR終端穩(wěn)壓器數(shù)據(jù)表.pdf》資料免費下載

2024-03-13 13:53:03 0

0 該內(nèi)存速度高達5600MT/s,并可同時兼容5200和4800 MT/s。據(jù)詳情頁介紹,其工作電壓僅為1.1V,相較于DDR4 3200內(nèi)存,性能提升幅度為1.5倍,且將于本月底開始出貨。

2024-03-13 11:43:05 91

91 電子發(fā)燒友網(wǎng)站提供《具有同步降壓控制器、2A LDO和緩沖基準的TPS51916完整DDR2、DDR3、DDR3L和DDR4存儲器電源解決方案數(shù)據(jù)表.pdf》資料免費下載

2024-03-13 11:24:34 0

0 電子發(fā)燒友網(wǎng)站提供《具有同步降壓控制器、2A LDO和緩沖基準的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4內(nèi)存電源解決方案數(shù)據(jù)表.pdf》資料免費下載

2024-03-13 11:13:44 0

0 電子發(fā)燒友網(wǎng)站提供《完整的DDR、DDR2和DDR3內(nèi)存電源解決方案同步降壓控制器數(shù)據(jù)表.pdf》資料免費下載

2024-03-13 10:16:45 0

0 DDR5內(nèi)存相對于DDR4有更高的內(nèi)部時鐘速度和數(shù)據(jù)傳輸速率,從而提供更高的帶寬。DDR5的傳輸速率可以達到6400MT/s以上,比DDR4的最高傳輸速率提高了一倍以上。

2024-03-12 11:23:34 118

118 DDR6和DDR5內(nèi)存的區(qū)別有多大?怎么選擇更好? DDR6和DDR5是兩種不同的內(nèi)存技術(shù),它們各自在性能、功耗、帶寬等方面都有不同的特點。下面將詳細比較這兩種內(nèi)存技術(shù),以幫助你選擇更適合

2024-01-12 16:43:05 2850

2850 使用SC584外擴DDR3,no_boot啟動模式,開發(fā)環(huán)境CCES-2.2.0版本,在線調(diào)試過程,程序可正常下載,但是在A5預(yù)加載過程中會出現(xiàn)SYS_FAULT拉高現(xiàn)象,經(jīng)實際匯編單步調(diào)試發(fā)現(xiàn)

2024-01-12 08:11:46

在最為重要的內(nèi)存顆粒上,根據(jù)軟件檢測,這款內(nèi)存采用了編號為“H5CG48AEBDX018”的SK海力士A-die顆粒,與市面上大部分DDR5 7600、DDR5 8000等高速率內(nèi)存使用的顆粒相同,這也意味著該內(nèi)存可能具備優(yōu)秀的超頻潛力。

2024-01-02 14:37:01 192

192

在DDR4年代,芝奇與阿斯加特成功完成逆襲,從原先的落落無名轉(zhuǎn)變?yōu)槿缃袷艿綇V大DIY玩家追捧的內(nèi)存廠商。

2023-12-29 10:41:00 247

247

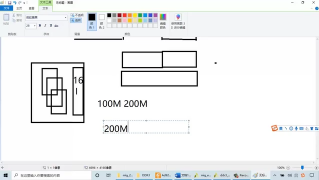

時鐘頻率:可通過倍頻技術(shù)升級的核心頻率。時鐘頻率可以理解為IO Buffer的實際工作頻率,DDR2中時鐘頻率為核心頻率的2倍,DDR3 DDR4中時鐘頻率為核心頻率的4倍。

2023-12-25 18:18:47 1188

1188

)

DDR3內(nèi)存條,240引腳(120針對每側(cè))

DDR4內(nèi)存條,288引腳(144針對每側(cè))

DDR5內(nèi)存條,288引腳(144針對每側(cè))

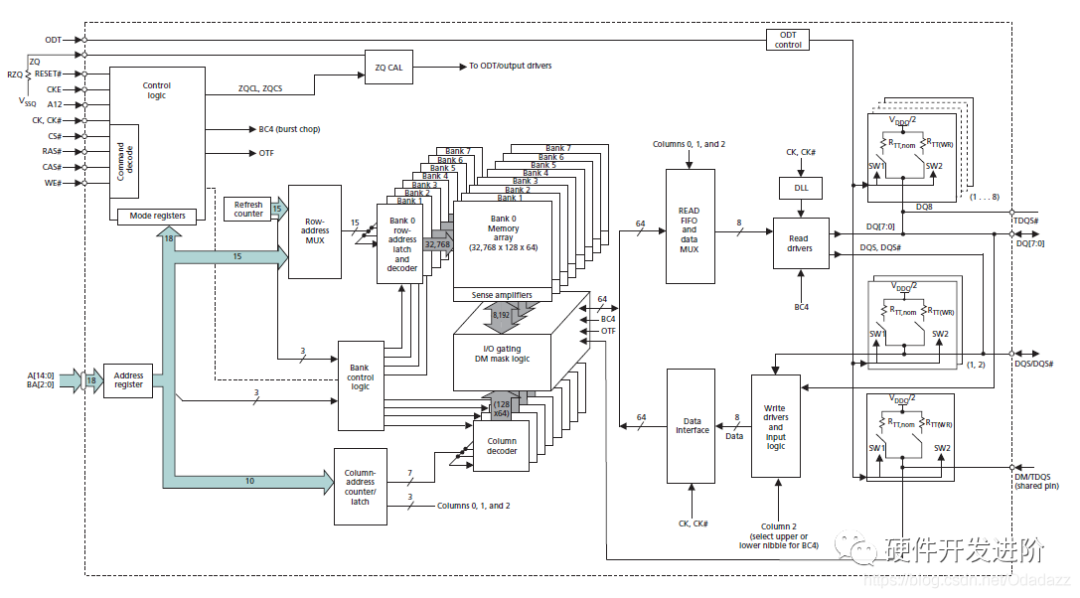

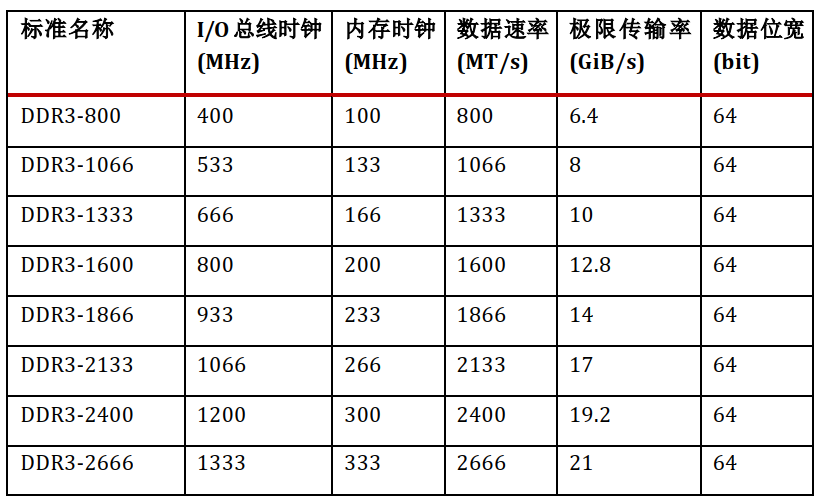

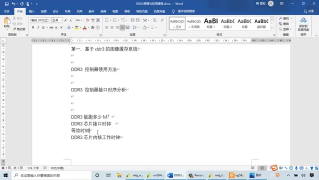

DDR芯片引腳功能如下圖所示:

DDR數(shù)據(jù)線的分組

2023-12-25 14:02:58

)

DDR3內(nèi)存條,240引腳(120針對每側(cè))

DDR4內(nèi)存條,288引腳(144針對每側(cè))

DDR5內(nèi)存條,288引腳(144針對每側(cè))

DDR芯片引腳功能如下圖所示:

DDR數(shù)據(jù)線的分組

2023-12-25 13:58:55

追風A60采用新一代DDR5內(nèi)存規(guī)格,相較DDR4,性能提升接近1倍。高配6000MHz頻率實現(xiàn)DDR4 3200MHz的1.6倍傳輸速度和1.9倍傳輸帶寬,讓用戶在使用臺電內(nèi)存條時獲得更快速、更流暢的電腦體驗。

2023-12-05 15:52:49 405

405

為滿足對高效內(nèi)存性能日益增長的需求,DDR5相比其前身DDR4實現(xiàn)了性能的大幅提升,具體為傳輸速度更快、能耗更低、穩(wěn)定性提高、內(nèi)存密度更大和存取效率提高等。

2023-12-05 10:50:40 211

211

法人方面解釋說:“標準型dram和nand目前由三星、sk hynix、美光等跨國企業(yè)主導,因此,中臺灣企業(yè)在半導體制造方面無法與之抗衡。”在ddr3 ddr3的情況下,臺灣制造企業(yè)表現(xiàn)出強勢。ddr3的價格也隨之上漲,給臺灣半導體企業(yè)帶來了很大的幫助。

2023-11-14 11:29:36 405

405 DDR4和DDR3內(nèi)存都有哪些區(qū)別? 隨著計算機的日益發(fā)展,內(nèi)存也越來越重要。DDR3和DDR4是兩種用于計算機內(nèi)存的標準。隨著DDR4內(nèi)存的逐漸普及,更多的人開始對兩者有了更多的關(guān)注。 DDR3

2023-10-30 09:22:00 3885

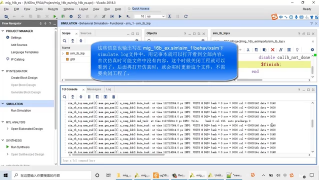

3885 DDR3是2007年推出的,預(yù)計2022年DDR3的市場份額將降至8%或以下。但原理都是一樣的,DDR3的讀寫分離作為DDR最基本也是最常用的部分,本文主要闡述DDR3讀寫分離的方法。

2023-10-18 16:03:56 516

516

摘要:本文將對DDR3和DDR4兩種內(nèi)存技術(shù)進行詳細的比較,分析它們的技術(shù)特性、性能差異以及適用場景。通過對比這兩種內(nèi)存技術(shù),為讀者在購買和使用內(nèi)存產(chǎn)品時提供參考依據(jù)。

2023-09-27 17:42:10 1088

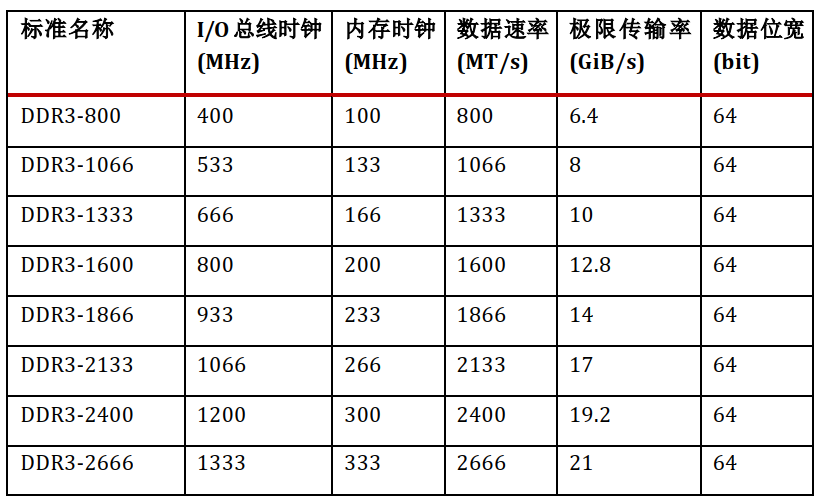

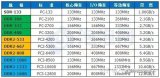

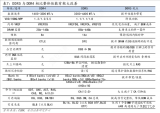

1088 我們在買DDR內(nèi)存條的時候,經(jīng)常會看到這樣的標簽DDR3-1066、DDR3-2400等,這些名稱都有什么含義嗎?請看下表。

2023-09-26 11:35:33 1922

1922

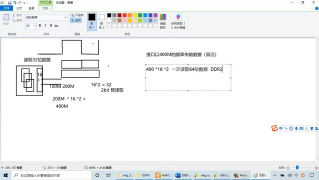

時,就需要外擴DDR SRAM二級存儲來滿足需求。

本期的主角盤古PGL50H FPGA就貼心的在核心板上,為我們配備了兩片DDR3的芯片,來完成二級存儲的需求。

兩片DDR3組成32bit的總線數(shù)據(jù)

2023-09-21 23:37:30

相對于DDR3, DDR4首先在外表上就有一些變化,比如DDR4將內(nèi)存下部設(shè)計為中間稍微突出,邊緣變矮的形狀,在中央的高點和兩端的低點以平滑曲線過渡,這樣的設(shè)計可以保證金手指和內(nèi)存插槽有足夠的接觸面

2023-09-19 14:49:44 1478

1478

以MT41J128M型號為舉例:128Mbit=16Mbit*8banks 該DDR是個8bit的DDR3,每個bank的大小為16Mbit,一共有8個bank。

2023-09-15 15:30:09 629

629

DDR3帶寬計算之前,先弄清楚以下內(nèi)存指標。

2023-09-15 14:49:46 2497

2497

一看到DDR,聯(lián)想到的就是高速,一涉及到高速板有些人就比較茫然。高速板主要考慮兩個問題點,當然其它3W,2H是基本點。

2023-09-15 11:42:37 757

757

在全默認設(shè)置的情況下,影馳HOF OC Lab幻跡S DDR5 8000內(nèi)存的工作速率為DDR5 4800,延遲設(shè)定為40-40-40-76,因此在這個設(shè)置下它的內(nèi)存性能并不突出,與普通的DDR5 4800內(nèi)存相當。

2023-09-15 10:40:42 750

750

內(nèi)置校準: DDR3和DDR4控制器通常具有內(nèi)置的校準機制,如ODT (On-Die Termination)、ZQ校準和DLL (Delay Locked Loop)。這些機制可以自動調(diào)整驅(qū)動和接收電路的特性,以優(yōu)化信號完整性和時序。

2023-09-11 09:14:34 420

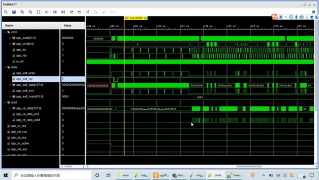

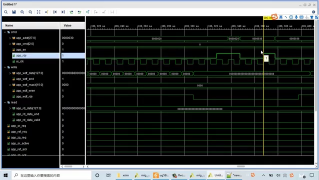

420 本文介紹一個FPGA開源項目:DDR3讀寫。該工程基于MIG控制器IP核對FPGA DDR3實現(xiàn)讀寫操作。

2023-09-01 16:23:19 741

741

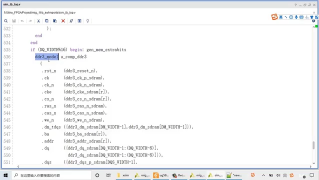

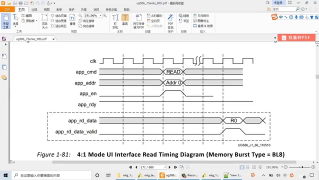

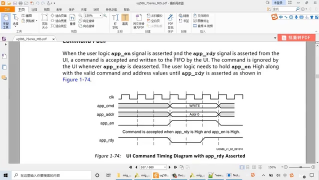

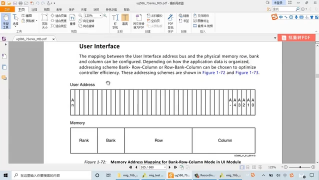

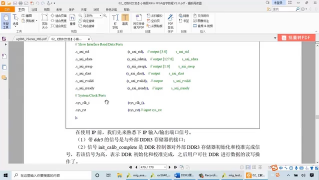

本文開源一個FPGA項目:基于AXI總線的DDR3讀寫。之前的一篇文章介紹了DDR3簡單用戶接口的讀寫方式:《DDR3讀寫測試》,如果在某些項目中,我們需要把DDR掛載到AXI總線上,那就要通過MIG IP核提供的AXI接口來讀寫DDR。

2023-09-01 16:20:37 1887

1887

的內(nèi)存速度和更低的功耗。 LPDDR4和LPDDR4X的主要區(qū)別在于功耗上的優(yōu)化。 LPDDR4內(nèi)存 LPDDR4內(nèi)存是一種第四代低功耗DDR內(nèi)存,是DDR4和DDR3的改進版本。該內(nèi)存的最大優(yōu)點是速度

2023-08-21 17:16:44 5949

5949 MCU200T的DDR3在官方給的如下圖兩份文件中都沒有詳細的介紹。

在introduction文件中只有簡略的如下圖的一句話的介紹

在schematic文件中也沒有明確表明每個接口的具體信息

2023-08-17 07:37:34

在配置DDR200T的DDR3時,一些關(guān)鍵參數(shù)的選擇在手冊中并沒有給出,以及.ucf引腳約束文件也沒有提供,請問這些信息應(yīng)該從哪里得到?

2023-08-16 07:02:57

復(fù)制Vivado工程路徑vivado_prj\at7.srcs\sources_1\ip\mig_7series_0下的mig_7series_0文件夾。粘貼到仿真路徑testbench\tb_ddr3_cache(新建用于DDR3仿真的文件夾)下。

2023-08-12 11:08:27 735

735 PH1A100是否支持DDR3,DDR4

2023-08-11 06:47:32

DDR5的主板不支持使用DDR4內(nèi)存。DDR5(第五代雙倍數(shù)據(jù)率)和DDR4(第四代雙倍數(shù)據(jù)率)是兩種不同規(guī)格的內(nèi)存技術(shù),它們在電氣特性和引腳布局上存在明顯差異。因此,DDR5內(nèi)存模塊無法插入DDR4主板插槽中,也不兼容DDR4內(nèi)存控制器。

2023-08-09 15:36:25 12794

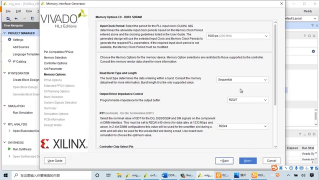

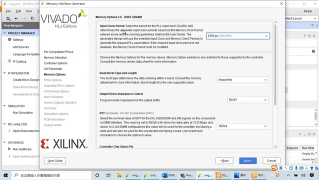

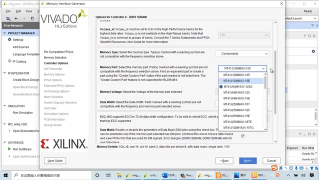

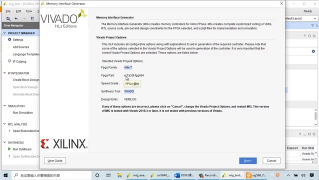

12794 xilinx平臺DDR3設(shè)計教程之設(shè)計篇_中文版教程3

2023-08-05 18:39:58

以下內(nèi)存設(shè)備:

?雙倍數(shù)據(jù)速率3(DDR3)SDRAM。

?低壓DDR3 SDRAM。

?雙倍數(shù)據(jù)速率4(DDR4)SDRAM。

2023-08-02 11:55:49

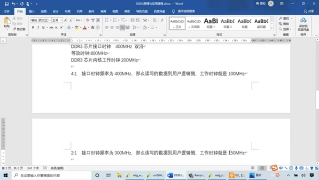

DDR是運行內(nèi)存芯片,其運行頻率主要有100MHz、133MHz、166MHz三種,由于DDR內(nèi)存具有雙倍速率傳輸數(shù)據(jù)的特性,因此在DDR內(nèi)存的標識上采用了工作頻率×2的方法。 ? DDR芯片

2023-07-28 13:12:06 1877

1877

電子發(fā)燒友網(wǎng)站提供《PI2DDR3212和PI3DDR4212在DDR3/DDR4中應(yīng)用.pdf》資料免費下載

2023-07-24 09:50:47 0

0 DDR是Double Data Rate的縮寫,即“雙倍速率同步動態(tài)隨機存儲器”。DDR是一種技術(shù),中國大陸工程師習慣用DDR稱呼用了DDR技術(shù)的SDRAM,而在中國臺灣以及歐美,工程師習慣用DRAM來稱呼。

2023-07-16 15:27:10 3362

3362

電子發(fā)燒友網(wǎng)站提供《由Alexa Skill驅(qū)動的淋浴式設(shè)備.zip》資料免費下載

2023-07-12 09:41:48 0

0 DDR3的速度較高,如果控制芯片封裝較大,則不同pin腳對應(yīng)的時延差異較大,必須進行pin delay時序補償。

2023-07-04 09:25:38 312

312

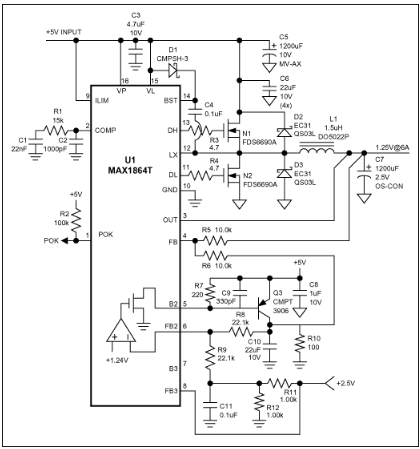

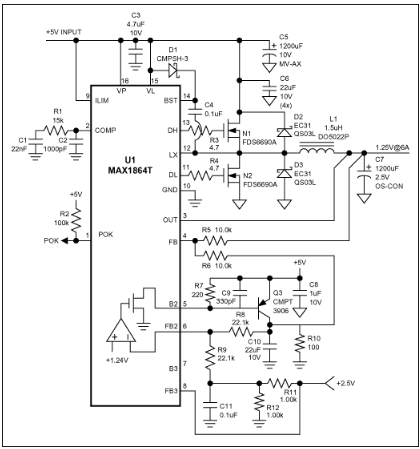

本設(shè)計筆記顯示了用于工作站和服務(wù)器的高速內(nèi)存系統(tǒng)的雙倍數(shù)據(jù)速率 (DDR) 同步 DRAM (SDRAM)。使用MAX1864 xDSL/電纜調(diào)制解調(diào)器電源,電路產(chǎn)生等于并跟蹤VREF的終止電壓(VTT)。

2023-06-26 10:34:36 549

549

1.DDR3 IP簡單讀寫測試實驗例程

1.1** 實驗?zāi)康?*

MES22GP 開發(fā)板上有一片 Micron 的 DDR3(MT41K256M16 TW107:P)內(nèi)存組件,擁有 16bit 位寬

2023-06-25 17:10:00

視頻圖形顯示系統(tǒng)理想的架構(gòu)選擇。視頻處理和圖形生成需要存儲海量數(shù)據(jù),F(xiàn)PGA內(nèi)部的存儲資源無法滿足存儲需求,因此需要配置外部存儲器。 ??? 與DDR2 SDRAM相比,DDR3 SDRAM帶寬更好高、傳輸速率更快且更省電,能夠滿足吞吐量大、功耗低的需求,因此

2023-06-08 03:35:01 1024

1024 和 DQS Gate Training

?DDR3 最快速率達 800 Mbps

三、實驗設(shè)計

a. 安裝 DDR3 IP 核

PDS 安裝后,需手動添加 DDR3 IP,請按以下步驟完成:

(1

2023-05-31 17:45:39

我正在使用帶有 ECC 芯片的 4GB DDR3 RAM 連接到 T1040 處理器 DDR 控制器。

我嘗試了這個序列,但未能成功生成 DDR 地址奇偶校驗錯誤:

步驟1:

ERR_INT_EN

2023-05-31 06:13:03

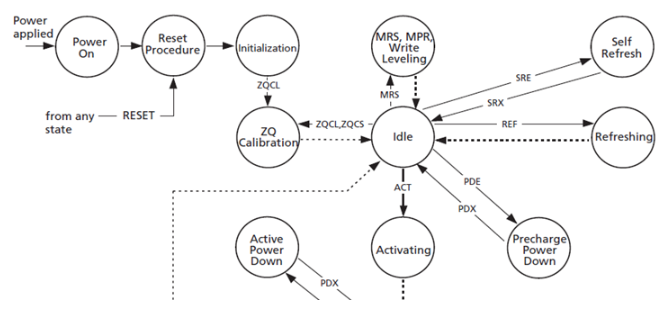

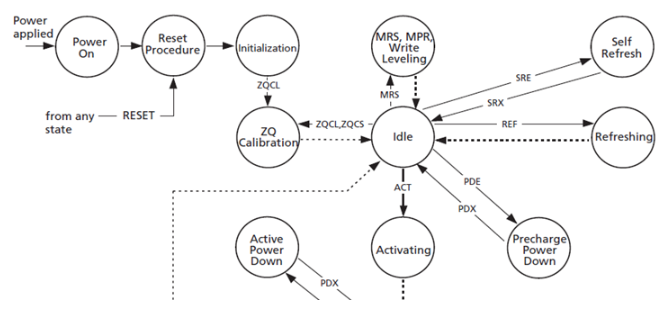

1 – DDR3 SDRAM JEDEC 標準 JESD79-3F 狀態(tài)圖和圖 2 – DDR4 SDRAM JEDEC 標準 JESD79-4 狀態(tài)圖所示。

2023-05-26 18:02:27 995

995

S32G3開發(fā)板上使用的ddr芯片是micro MT53E1G32D2FW-046 AUT: B

但是我們的開發(fā)板使用的是三星的芯片(K4FBE3D4HM THCL)。

如何查看 S32G3 支持的 DDR 芯片?。以及如何支持新的DDR芯片?

2023-05-23 07:15:48

Write Leveling 和 DQS Gate Training

?DDR3 最快速率達 800 Mbps

三、實驗設(shè)計

a. 安裝 DDR3 IP 核

PDS 安裝后,需手動添加 DDR3 IP,請按

2023-05-19 14:28:45

你好 :

專家,我們想使用S32R45和DDR3,你能幫我在哪里找到示例項目或用例嗎?

2023-05-17 08:13:46

DDR4內(nèi)存模塊支持單個64位通道(如果考慮ECC,則為72位通道)。相比之下,DDR5內(nèi)存模塊配備了兩個獨立的32位通道(40位ECC)。

2023-05-08 10:27:44 1330

1330 內(nèi)存是數(shù)據(jù)中心、服務(wù)器以及個人計算機等技術(shù)發(fā)展的重要組成。目前內(nèi)存的發(fā)展是由DDR技術(shù)路線引導,TE Connectivity(以下簡稱“TE”)經(jīng)歷了DDR1、DDR2、DDR3、DDR4的迭代

2023-05-06 17:33:42 1392

1392

在 i.MX6 SOLO 中有沒有辦法讀取芯片 DDR3 的大小?

2023-05-06 07:04:11

ls1046a ddr 內(nèi)存 8G 升級到 16G 硬件和軟件需要哪些改動 ..?

2023-04-10 06:21:57

DDR內(nèi)存1代已經(jīng)淡出市場,直接學習DDR3 SDRAM感覺有點跳躍;如下是DDR1、DDR2以及DDR3之間的對比。

2023-04-04 17:08:47 2867

2867

我們使用 10*MT40A1G16 獲得 16GB 內(nèi)存,一個 ddr 控制器連接 8GB。三個問題:1)在codewarrior ddr config上,我們應(yīng)該選擇什么dram類型?NoDimm

2023-04-03 07:24:21

SITE LICENSE DDR3 SDRAM ECP3

2023-03-30 12:01:46

IP CORE DDR3 SDRAM CTLR ECP3

2023-03-30 12:01:16

我一直在研究 BL2 上的 DDR 驅(qū)動程序,并注意到 *** 設(shè)置了對內(nèi)存區(qū)域的訪問,在研究 CW 腳本時也是如此。是否需要初始化 *** 才能訪問 DDR 內(nèi)存?我知道它不需要 MMU,但它與 TZ 一樣嗎?

2023-03-27 07:13:46

電子發(fā)燒友App

電子發(fā)燒友App

評論