ltc6803概述

LTC6803是一款第二代高壓電池監視器。2011年2月22日–凌力爾特公司(Linear Technology Corporation) 推出第二代高壓電池監視器LTC?6803,該器件面向混合動力/電動汽車(HEV)、電動汽車(EV)以及其他高壓、高性能電池系統。LTC6803是一款完整的電池測量IC,包含一個12位ADC、一個精確的電壓基準、一個高壓輸入多路復用器和一個串行接口。每個LTC6803都能測量多達12個串聯連接的獨立電池單元。該器件的專有設計使多個LTC6803能串聯疊置,而無需光耦合器或隔離器,從而允許對長串串聯連接電池中的每一節電池進行精確的電壓監視。

LTC6803芯片特點

可測量多達12 個串聯電池的電壓

可堆疊式架構

可支持多種電池化學組成和超級電容器

至相鄰器件的串行接口菊式鏈接

0.25% 的最大總測量誤差

專門針對符合ISO26262 標準的系統進行設計

可在 13ms 完成一個系統中所有電池的測量

無源電量平衡:

― 集成型電量平衡 MOSFET

― 能夠驅動外部平衡 MOSFET

具數據包誤差檢驗功能的 1MHz 串行接口

可在電池隨機連接的情況下保持安全

內置自測試功能電路

導線開路連接故障檢測

抗 EMI 的能力高

44 引腳 SSOP 封裝

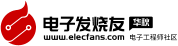

LTC6803的命令格式

LTC6803的應用領域

電動汽車和油電混合動力汽車

高功率便攜式設備

后備電池系統

電動自行車、摩托車、單腳滑行車

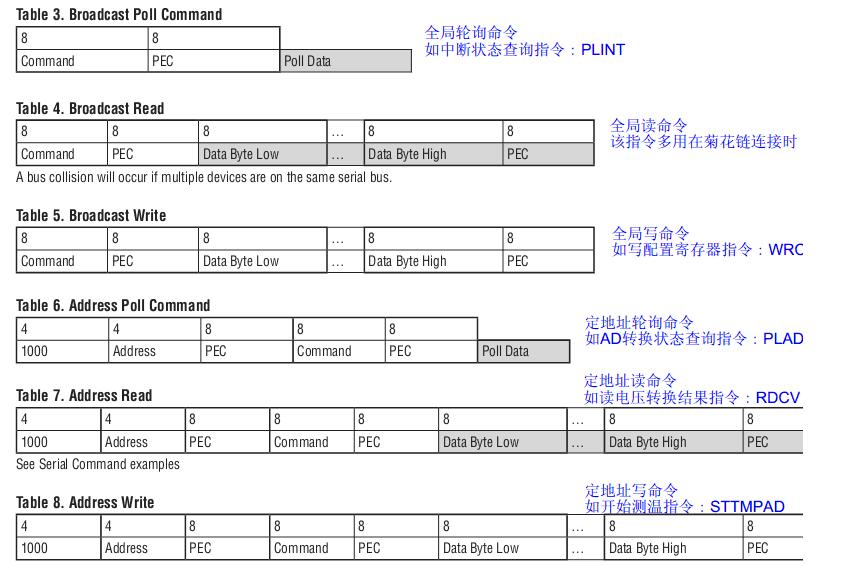

ltc6803絕對最大值

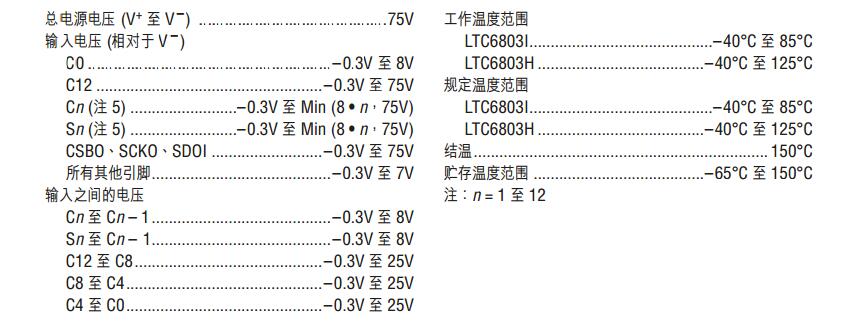

ltc6803引腳及功能

為了確保與LTC6802-1 的引腳兼容性,LTC6803-1 被配置為在內部將底端電池輸入(C0)與負電源電壓V-相連。LTC6803-3提供了一種獨特的引出腳配置,具有一個用于底端電池的輸入(C0)。這一簡單的引腳功能差異為提升第一節電池(cell 1)的測量準確度、增強SPI噪聲耐受性及簡化布線提供了可能。更多信息請見應用信息部分中標題為“在CO上進行開爾文(Kelvin) 連接的優勢”的相關描述。

CSBO (引腳1) :芯片選擇輸出(低態有效)。CSBO是芯片選擇輸入CSBI的一個緩沖版本。CSBO負責驅動菊鏈中的下一個IC。見“應用信息”部分中的“串行端口”。

SDOI(引腳2):串行數據1/0引腳。SDOI在其與菊鏈中下一個IC之間來回傳送數據。見“應用信息”部分中的“串行端口”。

SCKO (引腳3):串行時鐘輸出。SCKO是SCKI的一個緩沖版本。SCKO用于驅動菊鏈中的下一個IC。見“應用信息”部分中的“串行端口”。

V+(引腳4):正電源。引腳4可連接至電池組中的最高正電壓或一個隔離式電源。在正常工作條件下,V+必須大于電池組中的最高正電壓。當接至隔離式電源時,可簡單地通過斷開V+來關斷LTC6803。

C12、C11、C10、C9、C8、C7、C6、C5、C4、C3、C2、C1 (引腳5、7、9、11、13、15、17、19、21、23、25、27):C1至C12是用于監視電池電壓的輸入。對于LTC6803-1,底端電池的負端子連接至引腳V- (而對于LTC6803-3則連接至引腳CO)。次最低電壓連接至C1,依次類推。有關將電池連接至LTC6803-1和LTC6803-3的更多詳情,請見“應用信息”部分中的插圖。LTC6803能監視多達12節串聯連接的電池。串接的每節電池都必須具有一個大于或等于位于其下方之電池電壓的共模電壓。允許100mV的負電壓。

S12、S11、S10、S9、S8、S7、S6、S5、S4、S3、S2、S1 (引腳6、8、10、12、14、16、18、20、22、24、26、28):S1至S12引腳用于平衡電池組里的電池。如果串聯電池中的一節電池過度充電,則S輸出的內部可用于對該節電池進行放電。每個S輸出的內部具有一個用于放電N溝道MOSFET。見“方框圖”。該NMOS的最大導通電阻為20Q。應把一個外部電阻器與NMOS相串聯,以在LTC6803封裝的外部散逸熱量。當采用內部NMOS對電池放電時,應監視芯片溫度。見“應用信息”部分中的“功率耗散和熱停機”。此外,S引腳的內部還具有一個上拉PMOS。這使S引腳能用于驅動外部MOSFET的柵極,以獲得較高的放電能力。

C0 (LTC6803-3上的引腳29):底端電池的負端子。C0與V-形成了開爾文(Kelvin)連接,可消除V-印制線上的電壓降所產生的影響。

V- (LTC6803-1 上的引腳29/LTC6803-3 。上的引腳30):把V-連接至串聯電池組中的最負電壓。

NC(LTC6803-1上的引腳30/LTC6803-3.上的引腳31):該引腳未被使用并在內部通過109電阻連接至V-。它可被置于懸空狀態或連接至PCB上的V-。

VTEMP1、VTEMP2(LTC6803-1上的引腳31、32/LTC6803-3. 上的引腳32、33):溫度傳感器輸入。ADC負責測量VTEMPn上的電壓(相對于V7)并將測量結果存儲于TMP寄存器中。ADC測量以VREF引腳電壓為基準。因此,可以采用連接至VREF引腳的熱敏電阻與電阻器的簡單組合來監溫度。VTEMP輸入也可以是通用的ADC輸入。可測量介于0V至5.125V (相對于V-)的任何電壓。

VREF (LTC6803-1上的引腳33 / LTC6803-3上的引腳34):3.065V電壓基準輸出。該引腳應采用一個1pF電容器進行旁路。VREF引腳能驅動一個連接至V-的100k阻性負載。較大的負載應采用一個LT6003運算放大器或相似器件加以緩沖。

VREG (LTC6803-1上的引腳34 1 LTC6803-3上的引腳35):線性穩壓器輸出。該引腳應采用一個1pF電容器進行旁路。VREG能向一個外部負載提供高達4mA的電流。VREG引腳不吸收電流。

TOS (LTC6803-1.上的引腳 35/ LTC6803-3上的引腳36):電池組頂端輸入。當LTC6803-1或LTC6803-3是菊鏈中的頂端器件時,將TOS連接至VREG。否則,將TOS連接至V-。當TOS被連接至VREG時,LTC6803-1或LTC6803-3將忽略SD0I輸入,而且SCKO、CSBO被關斷。當TOS被連接至V一時,LTC6803-1或LTC6803-3預計數據將被傳送至SDOI引腳及從SDOI引腳輸出。

NC (LTC6803-1. 上的引腳36):不連接。

WDTB(引腳37):看門狗定時器輸出(低態有效)。如果連續1至2.5s未接收到有效命令,則WDTB輸出被置為有效。WDTB引腳是一個漏極開路NMOS輸出。當其被置為有效時,它將輸出下拉至V-并把配置寄存器復位至其默認狀態。

GPI01、GPI02(引腳38、39):通用輸入/輸出。通過把一個“0”寫入一個GPIO配置寄存器位,漏極開路輸出被啟動且該引腳被拉至V-。通過將邏輯“1”寫入配置寄存器位,對應的GPIO引腳呈高阻抗。需要一個外部電阻器將該引腳拉至高達VREG。通過讀取配置寄存器存儲單元GPI01和GPI02的信息,即可確定這些引腳的狀態。例如:倘若一個“0”被寫至寄存器位GPI01,則始終回讀一個“0”,這是因為輸出N溝道MOSFET將引腳38拉至V-。如果一個“1”被寫至寄存器位GPIO1,則引腳變至高阻抗。視引腳38上的電壓的不同,回讀一個“1”或“0”。LTC6803可通過GPIO接通1關斷其周圍的電路,或者從周圍的某個電路讀取邏輯值。GPIO引腳不用時應連接至V-。

VMODE (引腳40):電壓模式輸入。當VMoDE連接至VREG時,SCKI、SDI、SDO和CSBI引腳被配置為電壓輸入和輸出。這意味著這些引腳可接受標準的TTL邏輯電平。當LTC6803-1或LTC6803-3是菊鏈中的底端器件時,把VMoDE連接至VREG。當VMoDE連接至V-時,SCKI、SDI和CSBI引腳被配置為電流輸入和輸出,而SDO未使用。當LTC6803-1或LTC6803-3由菊鏈中的另一個LTC6803-1或LTC6803-3進行驅動時,把VMDE連接至/-。

SCKI(引腳41):串行時鐘輸入。倘若VMDE連接至VREG‘則SCKI引腳可連接至任何邏輯門(TTL電平)。假如VMODE連接至V-,那么SCKI必須由另一個LTC6803-1或LTC6803-3的SCKO引腳驅動。見“應用信息”部分中的“串行端口”。

SDI(引腳42) :串行數據輸入。如果VMODE連接至VREG,則SDI引腳可連接至任何邏輯門(TTL電平)。如果VMODE連接至V-,那么SDI必須由另一個LTC6803-1或LTC6803-3的SDOI引腳驅動。見“應用信息”部分中的“串行端口”。

SD0(引腳43):串行數據輸出。倘若VMODE連接至VREG,則SDO引腳是一個NMOS漏極開路輸出。在SDO上需要布設一個上拉電阻器。如果VMODE連接至V-,則不使用SDO引腳。對于那些非堆棧底端的器件,當從堆棧讀取數據時,SDI是一個數據輸出。見“應用信息”部分中的“串行端口”。

CSBI (引腳44) :芯片選擇(低態有效)輸入。假如VMoDE連接至VREG:則CSBI引腳可連接至任何邏輯門(TTL電平)。如果VMODE連接至V-,那么CSBI必須由另一個LTC6803-1或LTC6803-3的CSBO引腳驅動。見“應用信息”部分中的“串行端口”。

- 第 1 頁:ltc6803中文資料(ltc6803引腳及功能_特性參數及典型應用電路圖)

- 第 2 頁:ltc6803方框圖

本文導航

非常好我支持^.^

(6) 100%

不好我反對

(0) 0%

相關閱讀:

- [電子說] 速度與激情:為電動摩托車設計壽命更長的 16S-17S 鋰離子電池組 2024-03-14

- [電子說] 電池監控電路圖解 2024-02-10

- [電子說] 典型電池監視器電路圖分享 2024-02-12

- [電子說] 簡單的電池監視器電路圖 2023-12-18

- [電子說] 簡單的閃爍電池監視器電路圖 2023-08-22

- [電子說] 帶3個LED的汽車電池監視器電路圖 2023-08-18

- [電子說] 使用兩個晶體管的電池監視器電路 2023-07-27

- [電子說] 12V鉛酸電池監視器的電路圖 2022-06-01

( 發表人:姚遠香 )