1

內(nèi)部變量的聲明

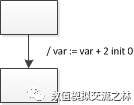

狀態(tài)圖環(huán)境內(nèi)部的變量使用init關(guān)鍵字聲明:

在這個例子中,我們引入了一個名為 var 的變量,類型為 int,初始值為 0。每次狀態(tài)圖執(zhí)行遍歷轉(zhuǎn)換時,變量將遞增 2。同一作用域中每個變量只能有一個init。

變量初始化的語法為:

varname:=expr0 init expr1

此表達(dá)式引入了一個名為 varname 的變量,其初始值在第二個表達(dá)式中給出(在 init關(guān)鍵字之后)。

從上述表達(dá)可以看出關(guān)鍵字 init 是用在過渡狀態(tài)線上。

2

內(nèi)部變量聲明的簡化寫法

如果賦值中使用的表達(dá)式與用于初始化的表達(dá)式相同,則可以使用簡化的語法:

我們在這里介紹兩個變量 x 和 y,它們在傳遞初始轉(zhuǎn)換時將被分配為零(整數(shù)或?qū)崝?shù))。

變量的類型取決于用于初始化它的值。例如,在這里,使用文字整數(shù) 0 和浮點(diǎn)文字 0.0 分別導(dǎo)致實(shí)際類型 int 和 real:類型確定自動執(zhí)行并最終在整個狀態(tài)圖中傳播(任何后續(xù)使用 x 和 y 都會傳播所涉及的表達(dá)式中的 int 和實(shí)數(shù)類型約束)。

注意:禁止將 int 變量與實(shí)變量混合和匹配。必須使用 to_real 和 to_int 函數(shù)進(jìn)行轉(zhuǎn)換。Int 常量可以在任何地方用作實(shí)常數(shù),但在從初始狀態(tài)過渡時。(看到?jīng)] to_real 和 to_int 又是兩個關(guān)鍵字)

3

變量的作用范圍

內(nèi)部變量的作用范圍也即是內(nèi)部變量的作用域。它們僅在狀態(tài)圖的某些部分可見。

變量在其復(fù)合狀態(tài)下可見,在下面的所有子復(fù)合(或并行)狀態(tài)下可見。

此示例中有三個不同的聲明變量,一個“y”變量僅在第一個復(fù)合狀態(tài)下可見,因?yàn)橛糜诼暶魉?init 關(guān)鍵字位于此狀態(tài)內(nèi)的轉(zhuǎn)換中。還聲明了兩個同名變量:“x”。一個在頂層和 Composite1 可見;另一個在 Composite2 中聲明,并隱藏先前聲明的變量。由于這種隱藏,Composite2 無法訪問在頂級聲明的變量 x。Composite 1 不會重新定義名為 x 的變量,因此可以訪問在頂級聲明的變量。

注意:狀態(tài)圖環(huán)境編譯器將在存在變量隱藏的情況下生成警告消息。(警告只是警告,但不是錯誤)

為了簡化不同變量的范圍,下表綜合了不同變量的范圍:

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8745瀏覽量

148059 -

信號處理器

+關(guān)注

關(guān)注

1文章

254瀏覽量

25351 -

有限狀態(tài)機(jī)

+關(guān)注

關(guān)注

0文章

52瀏覽量

10372 -

AMESIM

+關(guān)注

關(guān)注

1文章

15瀏覽量

11747

發(fā)布評論請先 登錄

相關(guān)推薦

有限狀態(tài)機(jī)有什么類型?

什么是有限狀態(tài)機(jī)呢

基于VHDL的MTM總線主模塊有限狀態(tài)機(jī)設(shè)計

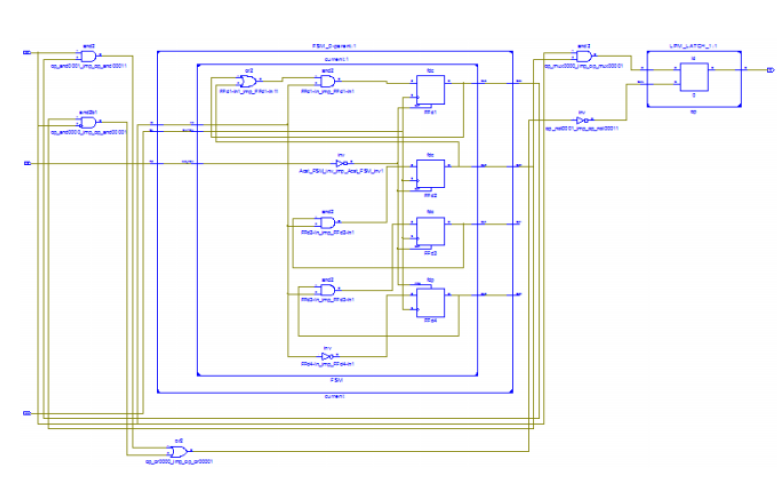

有限狀態(tài)機(jī)_FSM_的實(shí)現(xiàn)

有限狀態(tài)機(jī)的建模與優(yōu)化設(shè)計

VHDL有限狀態(tài)機(jī)設(shè)計-ST

初學(xué)者對有限狀態(tài)機(jī)(FSM)的設(shè)計的認(rèn)識

Linux編程之有限狀態(tài)機(jī)FSM的理解與實(shí)現(xiàn)

如何使用FPGA實(shí)現(xiàn)序列檢測有限狀態(tài)機(jī)

有限狀態(tài)機(jī)設(shè)計是HDL Designer Series的關(guān)鍵應(yīng)用

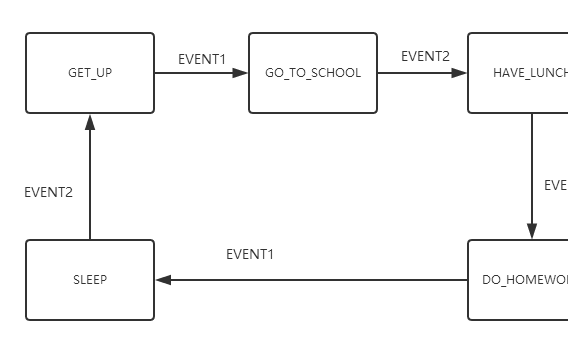

基于事件驅(qū)動的有限狀態(tài)機(jī)介紹

如何以面向?qū)ο蟮乃枷朐O(shè)計有限狀態(tài)機(jī)

AMEsim信號處理之有限狀態(tài)機(jī)內(nèi)部變量的聲明

AMEsim信號處理之有限狀態(tài)機(jī)內(nèi)部變量的聲明

評論