使用Cadence Allegro進行PCB設計時,經常用到Subdrawing功能進行走線和孔的復用,Subdrawing的孔和線避免不了與原用的線和孔進行重疊。

線重疊比較容易解決,但孔重疊就比較麻煩。

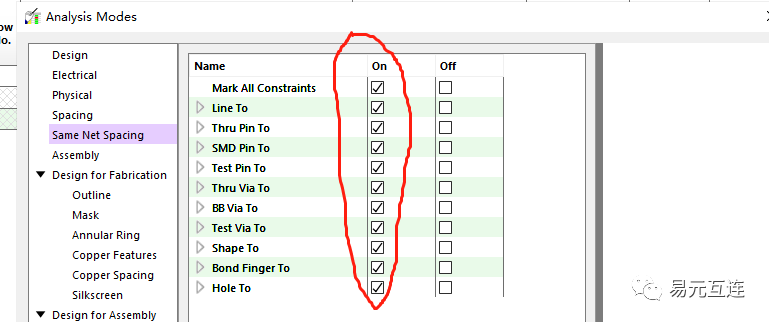

小易今天就碰到了這個麻煩,小易的規則是這樣設置的,首先把Same Net Spacing的檢查打開,如下圖所示;

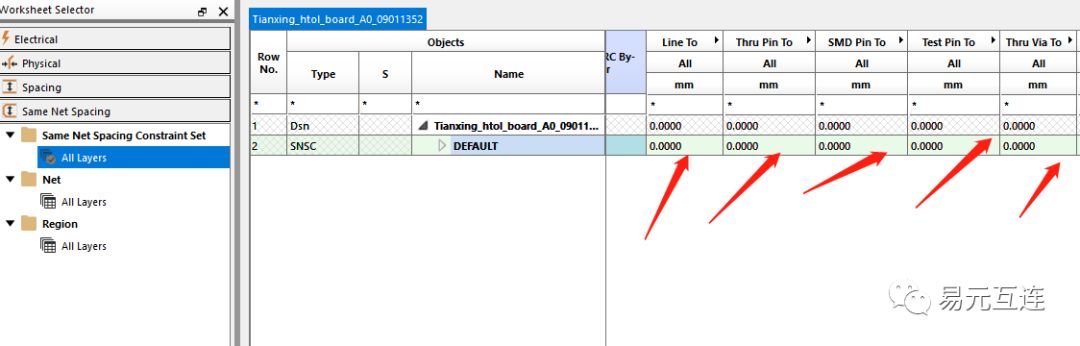

接著把Same Net Spacing的所有間距設置為0,如下圖所示;

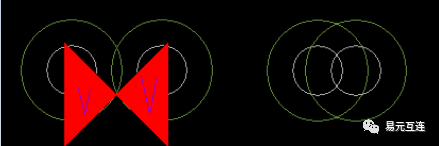

這樣,同網絡的VIA相交時,就會有DRC產生,如下左圖所示;但如果兩個VIA相交的更狠些,直到兩個Hole相交后,如下右圖所示,發現DRC就沒有了,這個就很奇怪了。

究其原因,Allegro在15.2版本之前,沒有做槽孔的功能,當時槽孔的做法就是把N個通孔通過Hole交叉疊加的方式來做出來的,如上右圖,板廠會將兩個Hole交叉的地方做成一個槽孔,這在Allegro的認知中,就認為這種做法是做成一個槽孔,所以就不會有DRC產生了。

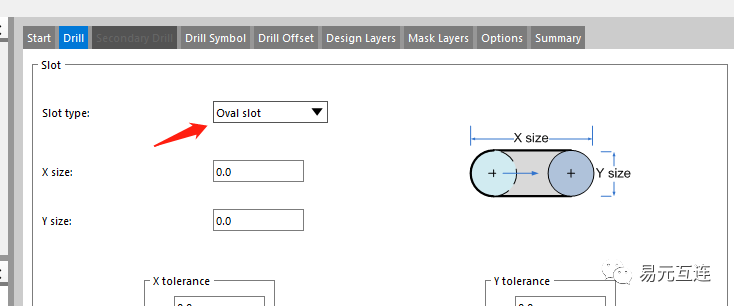

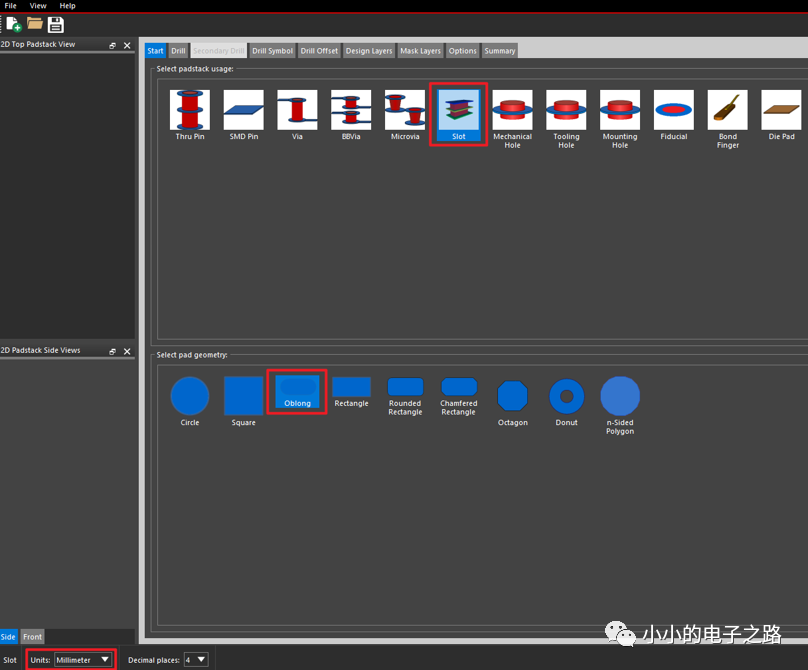

Cadencen Allegro發展到現在的2022版,已經不需要通過疊孔的方式來做槽孔了,如下圖所示,專門有做槽孔的選項。鉆孔重疊在PCB設計

中就不能允許存在了。但Cadence Allegro軟件本身又無法查出這種Hole相交的疊孔,也不知道Cadence公司為什么不更新這個檢測功能,有同仁知道的可以在文章后面幫忙發出來,在這里先謝了。

不過鉆孔重疊對DFM來說,卻是非常簡單的一個事,下面就用華秋DFM軟件來說明下檢查的方法。

第一步,不用出GERBER資料,直接硬干,打開PCB文件,就是這么強大;華秋DFM可以直接打開PCB文件,不需要每次都要繁瑣的反復出GERBER文件或ODB++文件;

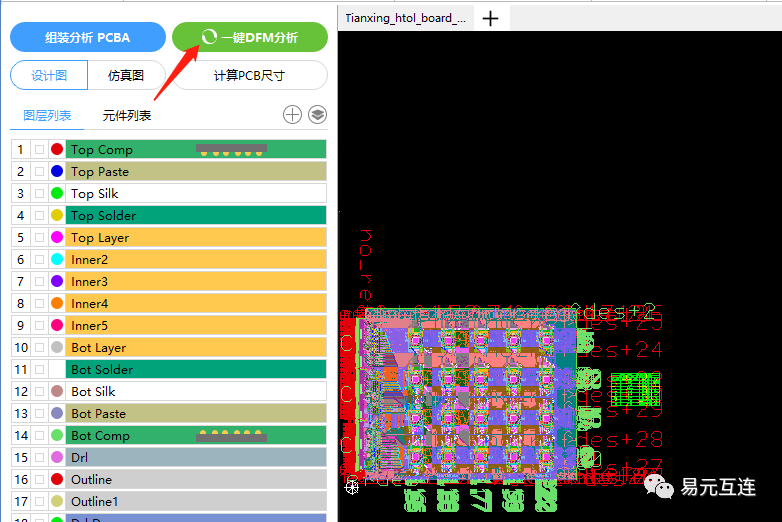

第二步,打開PCB文件后,直接點擊“一鍵DFM分析”按鈕,如下圖所示;

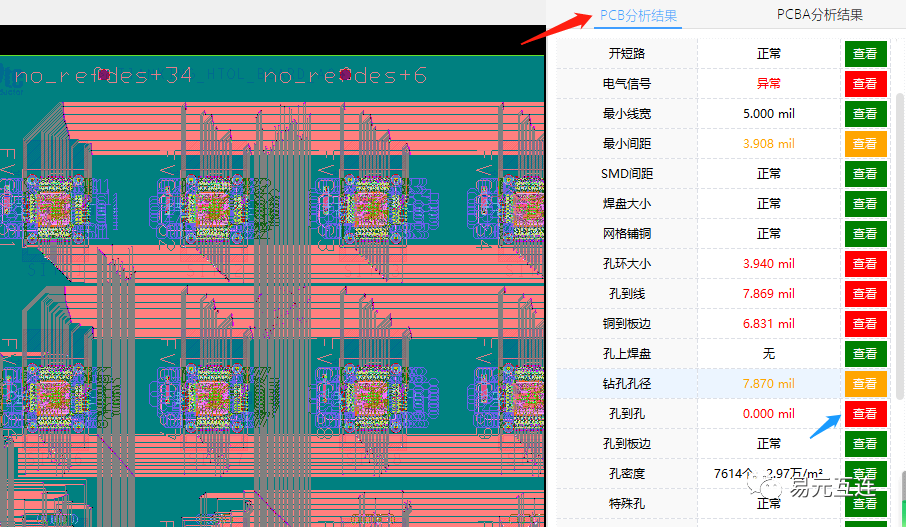

第三步,PCB的分析結果出現在右側,如下圖所示,孔到孔的間距出現紅色,間距0mil;

第四步,點擊右側紅色“查看”按鈕,就出現了一個檢查孔到孔的對話,點擊右側分析結果,會自動跳到相應的孔重疊的地方,如下圖所示;

第五步,根據檢查的結果,在PCB里進行更改,刪除多余的重疊孔。

-

Cadence

+關注

關注

65文章

930瀏覽量

142460 -

PCB設計

+關注

關注

394文章

4701瀏覽量

86356 -

DRC

+關注

關注

2文章

150瀏覽量

36361

發布評論請先 登錄

相關推薦

cadence 原理圖檢查工具

cadence allegro自動生成鉆孔

基于Cadence軟件DRACULA工具的LVS檢查

基于Cadence軟件DRACULA工具的DRC檢查

如何在Cadence Allegro軟件中制作槽孔焊盤

請問在Cadence中鉆孔重疊如何檢查呢?

請問在Cadence中鉆孔重疊如何檢查呢?

評論