引言

今天到手的是 Altera 的Cyclone? V系列FPGA,型號5CGTFD7D5F27C7N,一篇文章帶你解讀,該型號的基本屬性。

5CGTFD7D5F27C7N

5CGTFD7D5F27C7N該系列優(yōu)勢

Cyclone? V 5CGTFD7D5F27C7N采用臺積電的28納米低功耗工藝,具備高度集成的邏輯功能和差分信號處理能力。此外,它還包含了硬件內(nèi)存控制器和集成的收發(fā)器,支持最高達(dá)3.125 Gbps的數(shù)據(jù)傳輸速率。這種獨特的設(shè)計使得Cyclone? V不僅可以在工業(yè)自動化、無線通信和有線傳輸系統(tǒng)中得到廣泛應(yīng)用,還能在汽車電子和防務(wù)設(shè)備中發(fā)揮重要作用。

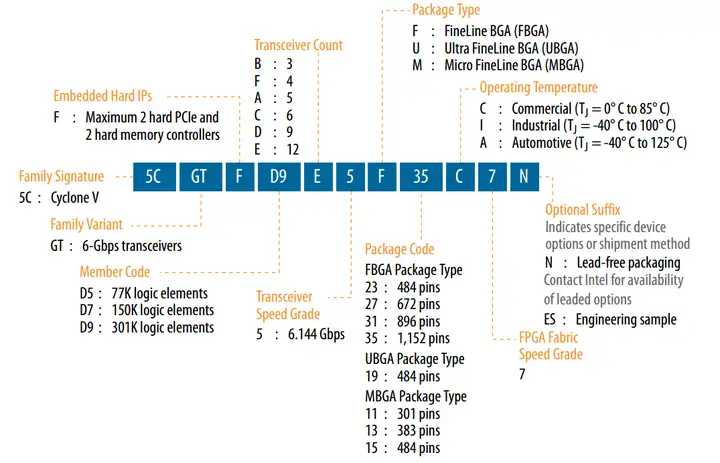

型號命名

型號命名

- (Family Signature) - “5C” 表明該芯片屬于Cyclone V系列。

- (Family Variant) - “GT” 指該芯片具有6-Gbps的收發(fā)器。

- (Embedded Hard IPs) - “F” 代表該型號芯片最多擁有2個硬件PCIe和2個硬件內(nèi)存控制器。

- (Member Code) - “D9” 表示該芯片具有301K邏輯元素。

- 收發(fā)器數(shù)量(Transceiver Count) - “E” 表示有12個收發(fā)器。

- 收發(fā)器速度等級(Transceiver Speed Grade) - “5” 表示收發(fā)器支持最高6.144 Gbps的數(shù)據(jù)速率。

- 封裝類型(Package Type) - “F” 表示芯片采用FineLine BGA (FBGA)封裝。

- 封裝代碼(Package Code) - “35” 表示該芯片具有1,152個引腳。

- 操作溫度(Operating Temperature) - “C” 表示商業(yè)級芯片,操作溫度范圍為0°C至85°C。

- 可選后綴(Optional Suffix) - “N” 表示該型號芯片采用無鉛封裝。

應(yīng)用領(lǐng)域與性能

憑借內(nèi)置的高速收發(fā)器和強大的信號處理能力,Cyclone? V FPGA在許多需要高速數(shù)據(jù)處理和高精度控制的應(yīng)用中表現(xiàn)出色,包括但不限于:

其他相關(guān)型號:

- 5CGTFD7B5M15C7N

- 5CGTFD7B5M15I7N

- 5CGTFD7C5F23C7N

- 5CGTFD7C5F23I7

- 5CGTFD7C5F23I7N

- 5CGTFD7C5U19C7N

- 5CGTFD7C5U19I7N

- 5CGTFD7D5F27C7N

- 5CGTFD7D5F27I7

- 5CGTFD7D5F27I7N

- 5CGTFD7D5F31C7N

- 5CGTFD7D5F31I7N

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605969 -

cpld

+關(guān)注

關(guān)注

32文章

1257瀏覽量

169629 -

Altera

+關(guān)注

關(guān)注

37文章

787瀏覽量

154160

發(fā)布評論請先 登錄

相關(guān)推薦

CPLD 與 ASIC 的比較

如何優(yōu)化 CPLD 性能

CPLD 優(yōu)勢與劣勢分析

CPLD 在嵌入式系統(tǒng)中的應(yīng)用

CPLD 應(yīng)用場景分析

CPLD 與 FPGA 的區(qū)別

什么是現(xiàn)場可編程邏輯陣列?它有哪些特點和應(yīng)用?

可編程邏輯器件TPLD1201數(shù)據(jù)表

5CGTFD7D5F27C7N Intel/Altera可編程邏輯器件(CPLD/FPGA)

5CGTFD7D5F27C7N Intel/Altera可編程邏輯器件(CPLD/FPGA)

評論