在傳統的工業控制應用中,由于工業控制計算機中集成了高性能的顯卡,故通常采用工業控制計算機+液晶顯示器的體系結構,可方便地實現以圖形和字符為主的人機界面。而在對實時性能和可靠性要求比較高的航空航天領域,通常要求液晶顯示器內部集成圖形顯示功能,以減輕主控處理器的負擔,并提高系統的實時性。重點介紹了如何利用FPGA實現基于Bresenham算法的2D圖形繪制(包括畫點、畫線、畫圓、畫橢圓),以及點陣字符和位圖在液晶屏上的顯示,并提出了顯示性能優化的一系列策略。經過仿真驗證和產品實際應用,該設計方法實現的液晶顯示模塊圖形和字符顯示功能穩定,性能良好,適合于航空航天領域高可靠性液晶顯示模塊的應用需求。

1 引 言

在傳統的工業控制應用中,多采用X86架構的工業控制計算機,計算機外置或集成顯卡輸出VGA/DVI視頻信號,由液晶顯示器完成顯示功能。在這種架構下采用軟件編程實現人機界面比較方便。而在嵌入式系統領域,尤其是航空航天儀表顯示設備的信息顯示領域,對顯示任務的可靠性和實時性要求很高。一方面需要減少設備內部的模塊及互聯總線,以提高設備的可靠性并降低功耗;另一方面,設備所選用的高可靠性處理器性能通常較低,需要專門的硬件加速器輔助完成顯示功能。硬件加速器主要完成字符顯示、圖表繪制及液晶屏驅動等功能,以減輕處理器的負擔,提高外部通信總線處理的實時性。基于FPGA的液晶顯示驅動及圖形加速器就是為了滿足顯示儀表設備而設計的。由于液晶顯示模塊內部集成了圖形和顯示功能,對設備主機處理器的性能要求大大降低,這樣就可以采用低性能、可靠性高的處理器來承擔顯示控制任務。

2 系統結構

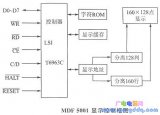

2.1 總體結構

儀表設備系統結構圖如圖1所示,由數據采集與通訊主機和液晶顯示模塊組成。

2.2 數據采集與通訊主機

數據采集與通訊主機采用51系列單片機,外接A/D采集、CAN等接口,主要完成數據采集、通信及向液晶顯示模塊發送頁面顯示命令等功能。

2.3 接口

液晶顯示模塊與設備主機間為RS422串行接口,通訊波特率為200kbit/s,數據傳輸協議是自定義的,由幀頭、數據包長度、命令、參數、校驗和構成,單個數據包最大長度為256字節。

幀頭:為0xEB、0x90兩字節,為整個數據幀的通訊過程提供同步功能;

字節長度:1字節,數據幀格式中指令的總字節數,最大不超過255字節。

指令:液晶顯示模塊操作指令內容,包括命令和參數,表1給出了部分操作指令格式及含義;

校驗:1字節,“字節長度”和“指令”字段的累加和,以校驗數據幀的正確性。

2.4 液晶顯示模塊

液晶顯示模塊,相當于小型液晶顯示終端,由液晶屏及其TCON 板、背光、圖形加速及顯示控制板組成。

液晶顯示模塊需完成的繪圖命令有:屏幕擦除(背景填充)、畫點、畫線、畫矩形、畫橢圓、畫圓、字符串顯示、自定義字顯示、圖片顯示、塊拷貝、塊粘貼等功能,以及字庫及圖片下載功能。除此之外,還有液晶屏亮度調節及狀態管理等命令。

2D繪圖指令定義見表1。

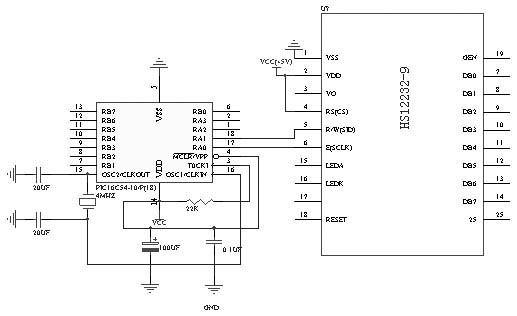

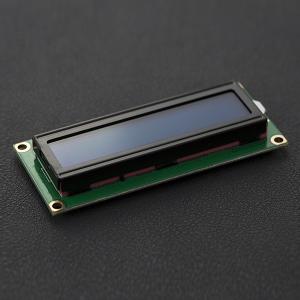

本設計選用的液晶屏為NEC公司的16.5cm(6.5in)TFT彩色液晶顯示屏,分辨率為640×480,液晶屏自帶TCON板,其接口為18bit數字RGB信號。

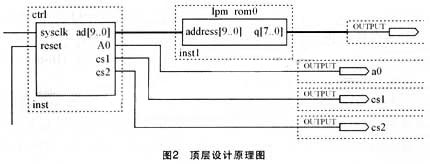

3 FPGA設計實現

FPGA在本設計中完成的工作主要是:一方面,進行數據接收并解析,根據命令進行圖形繪制操作,生成顯示幀存儲寫操作數據流,最后將要改寫的數據寫入SDRAM 存儲器中;另一方面,根據液晶屏同步信號時序要求,將幀存中顯示區的數據定時地讀出,生成液晶屏驅動數據流;其次,FPGA內部還具有PWM 信號生成模塊,可調節液晶顯示屏的亮度。

3.1 FPGA器件選型

FPGA選用Xilinx 2V3000系列[1],該器件具有28 672個LUT單元和個28 672個觸發器以及96個BlockRAMs,便于實現大規模控制邏輯及FIFO、Buffer等;另外,FPGA 內部具有DCM,可將外部65MHz時鐘轉為25MHz時鐘,用于液晶屏驅動時鐘,并可內部經分頻產生1kHz PWM信號,用于液晶屏背光亮度調節。

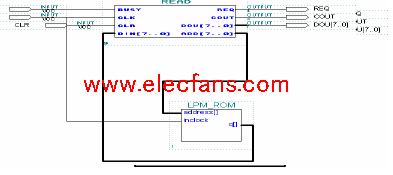

3.2 FPGA結構

FPGA內部結構如圖2所示。

3.2.1 命令接收解析模塊

數據命令(設備主機下發)以200kbit/s UART接口送入FPGA 中,FPGA 接收數據后,完成數據幀的識別、校驗。對于校驗無誤的數據幀,解析命令字的含義,并將對應的參數傳入相應的模塊中,啟動命令處理操作。

3.2.2 2D圖形加速模塊

所有的2D圖形繪制操作都可以分解為畫線段或畫橢圓等基本圖元操作,由于液晶屏為柵格顯示結構,基本圖元操作命令最終是轉化為打點操作。

畫線段和畫橢圓弧采用的是bresenham 算法[2]。該算法的基本原理是在進行線段繪制操作時,首先根據線段的斜率確定繪制的起點和方向,以確定每次在X 方向還是Y 方向上步進,然后每步進一步,確定在另一個方向上的增量,保持不動或者增1、減1,最后輸出該點坐標,流程圖如圖3所示。

如圖4所示,繪制一條從(0,0)至(18,6)的線段,第一個點為(0,0),由于dx>dy,則在x 方向上遞進,每個時鐘周期x 坐標加1。根據bresenham

算法,初始判決式為d1=dy×2-dx=6×2-18=-6<0,則第2個點(1,0),同時d2=d1+dy×2=6>0,則y++,輸出第3個點為(2,1),依次輸出下一個點,直到輸出最后一個點(18,6)。

同樣在進行橢圓或者圓繪制操作時,也采用了bresenham算法。在FPGA 中實現時,采用狀態機的編碼方式,以繪制圓心為(x0,y0)、長半軸為a、短半軸為b的橢圓為例,其狀態轉移流程圖圖如圖5所示。圖中CALC_A和CALC_B狀態分別為計算1/4橢圓弧中的a軸方向和b 軸方向的像素點。

畫線時的數據運算只有乘以2和加法,乘以2通過將數據左移1位,末位補0來實現。

在進行橢圓繪制時,乘法操作采用的是FPGA內部的MULT18X18S乘法單元,先將算式中的浮點數通過移位運算放大2n倍數轉換為定點數,計算得到的結果再通過截掉最低的n 位,相當于除以2n。通過這種方法避免了在FPGA 中做硬件除法,同時提高了繪圖效率。

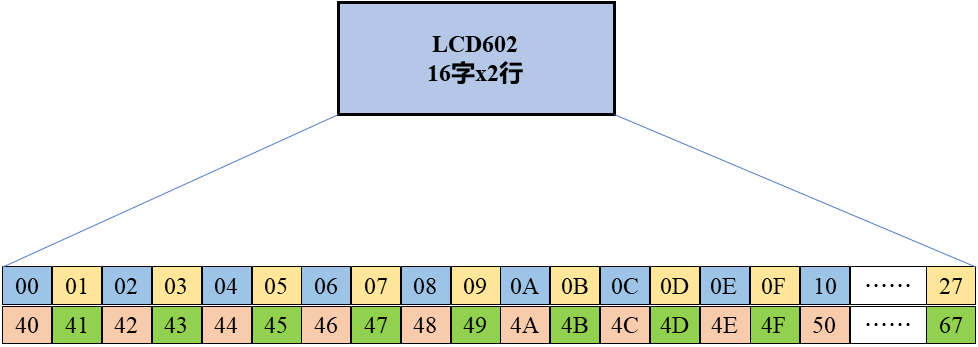

3.2.3 字符及圖片顯示加速模塊

在該設計中,液晶屏上顯示的字符為點陣字符。該字符庫是通過串行通訊接口(RS422)預置在FLASH 中的,字庫為預先轉換好的GB2312點陣字庫。本設計中采用了兩種規格大小的標準字庫,西文為黑體8×16和16×32,漢字為16×16及32×32。除此之外,用戶還可下載自定義的字庫,點陣大小最大可以為256×256,字庫可在屏幕上任意位置為起始點顯示。

預置圖片為256色BMP圖片,最大不超過屏幕分辨率(640×480),可以在屏幕上任意位置為起始點顯示。

字符和圖片在數據結構上具有相似性,均為點陣數據。

在顯示時,根據顯示命令,首先從存儲單元中獲取欲顯示的字符或圖片的點陣數據。對于字符,其點陣數據中的“0”表示不顯示,“1”表示顯示,然后向顯示坐標位置對應的地址空間中依次寫入顏色值。對于不需要寫入的像素點,在寫操作時,使用SDRAM 的寫屏蔽功能,每完成一行,地址切換到下一行,直至寫操作結束。

3.2.4 液晶屏數據流生成模塊

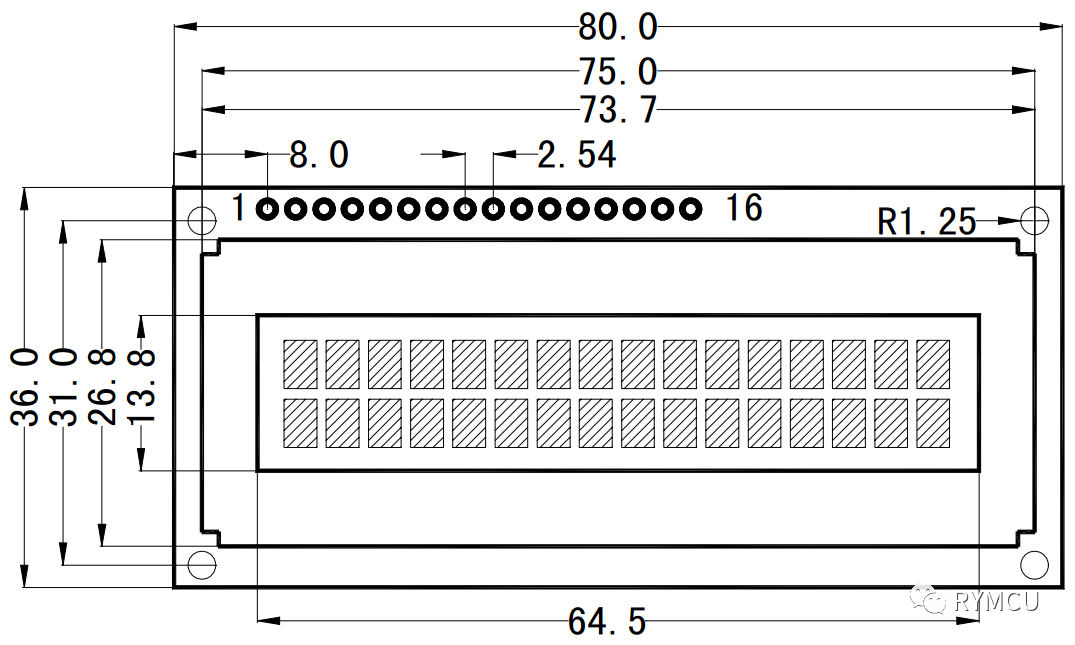

本設計中選用的液晶屏型號為NEC公司的NL6448-BC20-20[3],接口為LVTTL 數字RGB接口,包括R、G、B(每色為6bit)、HS、VS、DE、CLK等信號。

該液晶屏有兩種時序模式,固定時序模式和DE信號模式。固定時序模式下,液晶屏有效數據起始點是以HS、VS邊沿為參考的固定數值,而DE信號模式下,有效數據范圍是以DE信號為參考的。本設計中選擇了DE模式,每行中DE為高電平的第一個周期對應第一個有效數據。

液晶屏數據生成設計框圖如圖6所示。該模塊采用DCM 生成25MHz像素時鐘,并采用兩個計數器(行計數器和列計數器)生成DE信號[4-5],根據液晶屏時序要求,每行總共800個時鐘,有效像素點為640個時鐘;每列總共525行,有效數據區域為480行。在FPGA設計中,行計數器在像素時鐘下計數,從0計數到799后,輸出HS脈

沖,同時計數值回到0重新進行下一輪的計數;列計數器以HS信號脈沖為計數條件,從0計數到524行后,輸出VS脈沖,同時計數值回到0。

將行計數值定義為h_cnt,列計數值定義為v_cnt,數據有效信號DE設計為:

數據讀取模塊根據HS信號從SDRAM 存儲器中讀取一行有效數據到FIFO中,并采用DE信號作為FIFO的讀使能信號,將FIFO中的數據取出,生成18bit RGB數字信號送給液晶屏TCON板,驅動液晶屏輸出顯示畫面。

3.2.5 SDRAM 控制器

采用的SDRAM 容量為32M×32bit,設計的工作頻率為65 MHz,SDRAM 中劃分為多個區域:顯示頁面區、繪制操作頁面區、字庫區、圖片區等。

SDRAM 器件在進行讀寫操作時,需要先激活一行,然后在該行內,針對某個列地址進讀/寫操作,操作完畢后,需要進行預充電以關閉該行,同時,SDRAM 需要定期地進行刷新以保持其內部數據穩定不丟失。用FPGA 實現的SDRAM控制器就是為了實現提供一個便于上層讀寫訪問的簡單接口。

3.2.6 FLASH控制器

采用的FLASH容量為16M×16bit的NOR FLASH。FLASH 主要用于存儲字庫和圖片,內部數據可通過液晶顯示模塊數據通信口進行下載。

FLASH 接口為異步接口,在進行讀操作時,其時序相對簡單,類似于ROM。而在進行寫操作時則相對復雜,在寫FLASH 之前,先確認扇區為空,如果不為空,則需要先擦除。

3.2.7 存儲仲裁器

存儲仲裁器模塊結構如圖7所示,在同一時間,SDRAM 只能為其中一個模塊提供數據讀或寫操作。該模塊的設計是為了解決多模塊同時訪問SDRAM 或FLASH 時的優先級控制,以及提供排隊訪問的機制。該模塊中采用了標志位In-QueueFlag[2∶0]來分別記錄各模塊的狀態請求,并分別給出應答信號,以控制其對于SDRAM的讀寫訪問。

在FPGA設計中,由于液晶屏數據生成模塊對數據的及時性要求最高,給予其最高的優先級,在SDRAM接口空閑的情況下,優先處理InQueue-Flag[0]=1的請求,處理完畢后,InQueueFlag[0]清0。如果InQueueFlag[0]=0,則檢查InQueue-lag[1]是否為1,依次直至所有標志位為0。

4 優化系統性能的幾點設計

4.1 采用雙圖層、多頁面的設計

顯示屏在顯示時,具有前景和背景兩個圖層。在繪圖過程中,可進行切換[6]。

該顯示模塊在設計時,存儲區中開辟了10個操作頁面和顯示頁面。正常使用情況下,在后臺頁面進行繪圖操作,繪制完成后,將顯示頁面切換至該頁面。這樣可避免因繪圖操作對內存數據更新而引起的顯示不流暢感。

4.2 256色調色板設計

液晶屏有144種顏色,但對于圖形顯示屏而言,實際應用中并不需要這么多種色彩,256色已經可以滿足應用要求。在FPGA 內部,使用BlockRAM 建立了一個256色的調色板,每種色號對應一個RGB顏色值。

如果每個像素都存儲RGB值,則每像素需要18位。而采用256色,每個像素點的顏色只需要用8位來表示,由此可見,采用256色調色板的設計可以減小一半以上的內存帶寬需求。

4.3 緩存設計

在進行繪圖和字符、圖片等顯示操作時,每次寫入SDRAM 內存的數據,不是立即寫入的。而是先將要操作的SDRAM 地址及其數據暫存在buffer中,由專門的模塊負責將其寫入SDRAM中。這樣的設計有兩個好處,一是減少了對存儲器的頻繁讀寫,存儲器讀寫效率提高;另一方面,繪圖模塊無需等待數據寫入,便可繼續進行繪圖操作,大大提高了繪圖效率,從而提升了整個顯示模塊的性能。

4.4 高效率的SDRAM 控制器

用FPGA 實現的SDRAM 控制器[7-8],其核心是控制好SDRAM 讀寫命令給出的時機,并定時刷新SDRAM,同時提供方便的用戶接口給其他模塊使用。

另外,由于SDRAM 的特性,進行單字節操作時,其效率很低。經過分析,在65MHz時鐘下,寫入1個字節,至少需要8個時鐘周期,包括激活命令、寫命令、預充電命令以及等待時間,效率只有12.5%。

本設計中使用Burst操作,在Fullpage操作時,其讀寫效率會大大提高,接近97%。

4.5 FLASH數據校驗機制

為了保證存儲在FLASH區域中數據的完整性,系統在每次啟動時,會發送相關的自檢命令檢查FLASH 數據的完整性,并將自檢信息顯示在液晶屏上,以保證字庫、圖片數據的正確性。

5 仿真及測試結果

采用ModelSim6.2g對本設計進行了功能和時序仿真,仿真了屏幕擦除、畫線、畫圓和字符顯示等指令的性能情況。如圖8中(a)、(b)圖所示,圖中,cmd信號為指令(詳見表1),start_FBM、start_PCG是指令操作時的起始信號,圖中還給出了SDRAM 信號線。從圖中可以看到,cmd信號從0x00變到0x42表明開始進行擦除操作,由0x42切換到0x35表明擦除操作結束,開始執行畫線命令。可以看到在屏幕擦除操作過程中SDRAM 信號線CS、RAS、CAS上信號不斷變化,此時SDRAM 執行寫操作。

仿真結果表明,在65MHz時鐘頻率下,典型操作時間為:擦除整屏(640×480)耗時為2 910.6μs;畫一條長度為100的斜線段,耗時為14.0μs;繪制一個直徑為10的圓,耗時為13.6μs;顯示一個16×16大小的點陣漢字,耗時為44.1μs。

本設計實現的液晶顯示模塊在典型應用情況下,每秒約有250條繪圖命令,包含了屏幕擦除及大量畫線及字符串顯示操作。經仿真測試,在該使用情況下,SDRAM 讀寫占用率約為21%。

在RS422數據總線滿負荷情況下,每秒最大接收10k字節數據,最多為5k個漢字顯示,估算SDRAM 讀寫占用率約為30%,資源利用仍有足夠的余量。

由此可見,采用本設計的液晶顯示模塊在典型工況和數據總線滿負荷情況下,均有足夠的余量能夠高效地完成上位機發送的作圖命令,不會造成顯示遲滯。

該液晶顯示模塊已應用于飛行器儀表顯示系統中,并成功完成了飛行任務。

6 結 論

采用基于FPGA 圖形和字符加速的液晶顯示模塊,可以較好地滿足航空航天領域中高可靠性儀表顯示設備中低性能微處理器作為主機,而液晶顯示模塊作為顯示終端的應用需求,減輕了處理器及顯示控制軟件的復雜度。當然,本設計的部分性能指標還有待提高,為了適應高分辨率、大尺寸TFT液晶屏的要求,需要提高FPGA 運行頻率,同時采用DDR/DDR2SDRAM 等高速存儲器件。

電子發燒友App

電子發燒友App

評論